# GTI 5G Device RF Component Research Report

## GTI 5G Device RF Component

# **Research Report**

| Version:           | V1.0                                                                                                         |

|--------------------|--------------------------------------------------------------------------------------------------------------|

| Deliverable Type   | <ul> <li>□ Procedural Document</li> <li>√ Working Document</li> </ul>                                        |

| Confidential Level | <ul> <li>✓ Open to GTI Operator Members</li> <li>✓ Open to GTI Partners</li> <li>□ Open to Public</li> </ul> |

| Working Group      | Terminal WG                                                                                                  |

| Task               |                                                                                                              |

| Source members     |                                                                                                              |

| Support members    |                                                                                                              |

| Editor             | China Mobile, Qorvo, HiWafer, Soitec, Skyworks, TAIYO<br>YUDEN, Murata, VanChip                              |

| Last Edit Date     | Feb. 2 <sup>nd</sup> , 2018                                                                                  |

| Approval Date      | <mark>Feb. 9<sup>th</sup> , 2018</mark>                                                                      |

**Confidentiality**: This document may contain information that is confidential and access to this document is restricted to the persons listed in the Confidential Level. This document may not be used, disclosed or reproduced, in whole or in part, without the prior written authorization of GTI, and those so authorized may only use this document for the purpose consistent with the authorization. GTI disclaims any liability for the accuracy or completeness or timeliness of the information contained in this document. The information contained in this document may be subject to change without prior notice.

## **Document History**

| Date           | Meeting # | Version # | Revision Contents                          |

|----------------|-----------|-----------|--------------------------------------------|

| 02-02-2018     | #21       | v1.0      | GTI 5G Device RF Component Research Report |

| DD-MM-YYY<br>Y |           |           |                                            |

## Table of Contents

| 1 | Exec  | utive Su | ummary                                                         | 7  |

|---|-------|----------|----------------------------------------------------------------|----|

| 2 | Abb   | reviatio | ns                                                             | 8  |

| 3 | Intro | oduction | ٩                                                              | 10 |

| 4 | Refe  | rences   |                                                                | 12 |

| 5 | 5G [  | Device R | RF Component Industry Status                                   | 15 |

| 6 | Sub-  | 6GHz 5   | G Device RF Component                                          | 18 |

|   | 6.1   | Sub-6    | GHz 5G Power Amplifier                                         | 18 |

|   |       | 6.1.1    | Existing Mobile Device Commercial Power Amplifier              | 19 |

|   |       | 6.1.2    | Sub-6GHz 5G Power Amplifier Design                             | 22 |

|   | 6.2   | Sub-6    | GHz 5G Filter                                                  | 33 |

|   |       | 6.2.1    | Existing Mobile Device Commercial Filter                       | 33 |

|   |       | 6.2.2    | 3.3GHz-4.2GHz 5G Filter Design                                 | 41 |

|   |       | 6.2.3    | 4.4GHz-5GHz 5G Filter Design                                   | 45 |

|   | 6.3   | Sub-6    | GHz 5G Low Noise Amplifier                                     | 46 |

|   |       | 6.3.1    | Existing Mobile Device Commercial Low Noise Amplifier Products | 46 |

|   |       | 6.3.2    | Sub-6GHz 5G Low Noise Amplifier Design                         | 47 |

| 7 | mm    | Wave 50  | G Device RF Component                                          | 49 |

|   | 7.1   | mm₩      | Vave 5G Power Amplifier                                        | 49 |

|   | 7.2   | mm₩      | Vave 5G Filter                                                 | 51 |

|   | 7.3   | mm₩      | Vave 5G Low Noise Amplifier                                    | 53 |

|   | 7.4   | Switc    | hes for mmWave                                                 | 54 |

|   |       | 7.4.1    | What makes a 'Great' 5G Switch?                                | 54 |

|   |       | 7.4.2    | SOI Technology for 5G Switching                                | 55 |

| 8 | Rela  | ted 'Bla | ck Technologies'                                               | 55 |

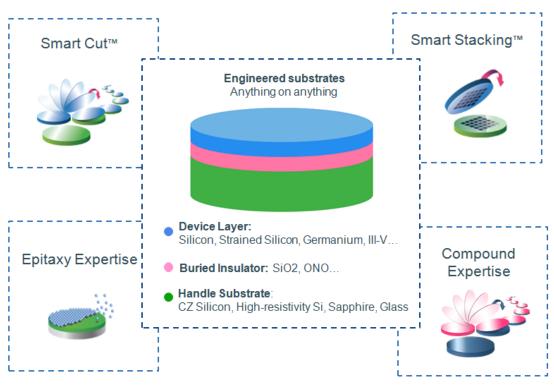

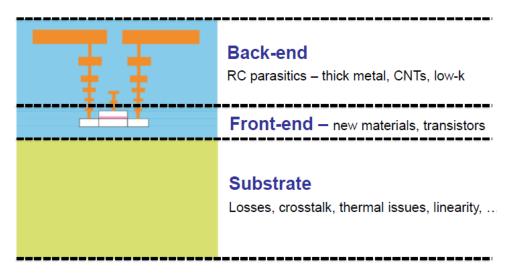

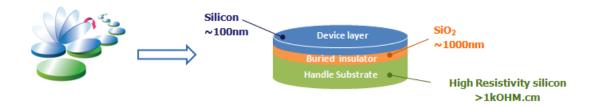

|   | 8.1   | Engin    | eered Substrate                                                | 55 |

|   |       | 8.1.1    | What is 'Engineered Substrate'?                                | 55 |

|     | 8.1.2 | Why do we need 'Engineered Substrate'?5         | 7  |

|-----|-------|-------------------------------------------------|----|

|     | 8.1.3 | Application 6                                   | 0  |

| 8.2 | Engir | neered Substrate: 'Anything on Anything'6       | 1  |

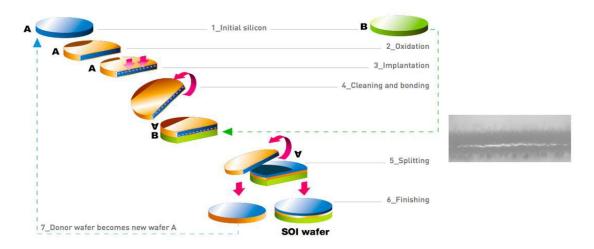

|     | 8.2.1 | Smart Cut <sup>™</sup> 6                        | 2  |

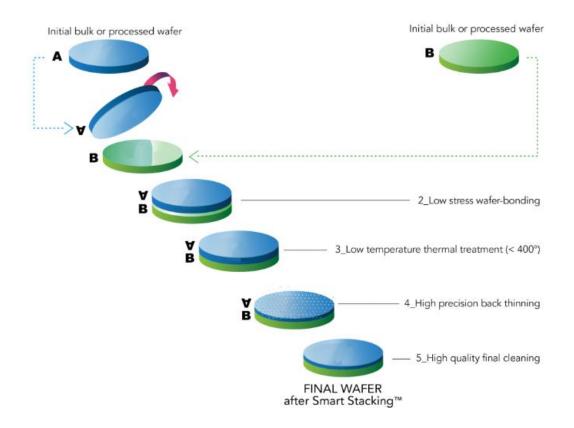

|     | 8.2.2 | Smart Stacking™6                                | 4  |

|     | 8.2.3 | Epitaxy 6                                       | 5  |

| 8.3 | СМО   | 9S on SOL 6                                     | 6  |

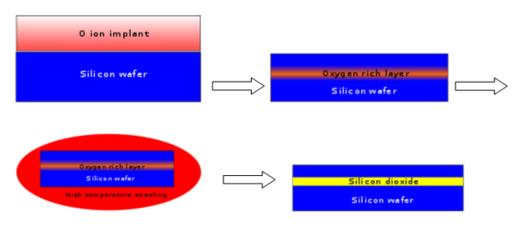

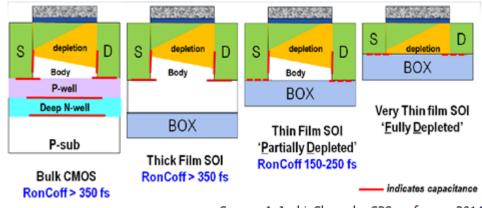

|     | 8.3.1 | CMOS on SOI basics                              | 7  |

|     | 8.3.2 | Basic SOI Advantages 6                          | 8  |

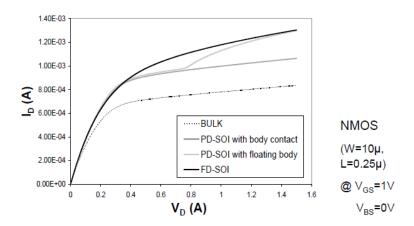

|     | 8.3.3 | PD-SOI and FD-SOI – Definition 6                | 9  |

|     | 8.3.4 | Floating body and Body contact7                 | 0  |

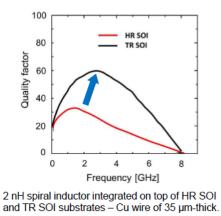

| 8.4 | СМО   | 9S on SOI for RF7                               | '1 |

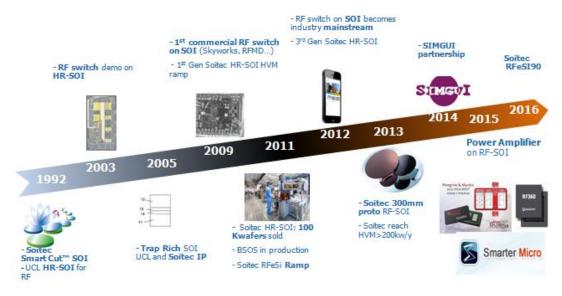

|     | 8.4.1 | RF-SOI                                          | '1 |

|     | 8.4.2 | PD-SOI for RF                                   | 1  |

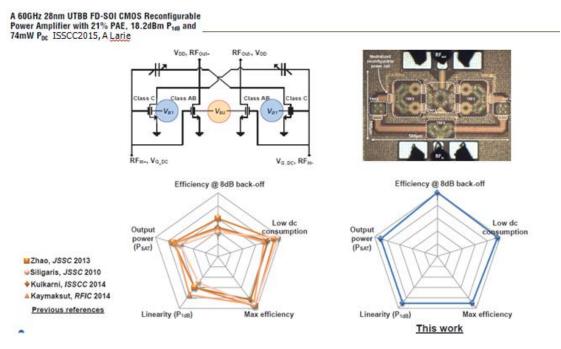

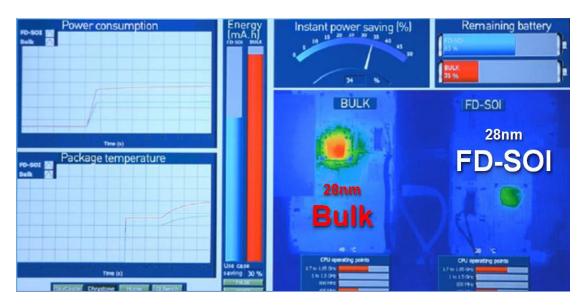

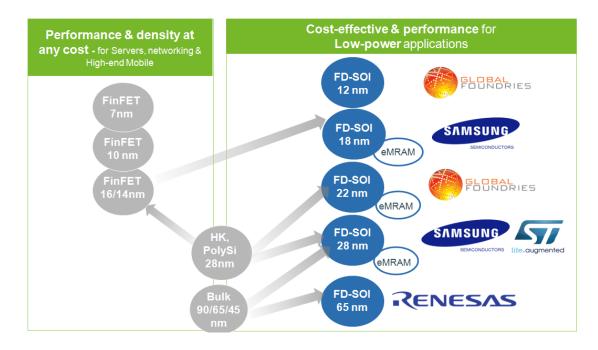

|     | 8.4.3 | FD-SOI                                          | 3  |

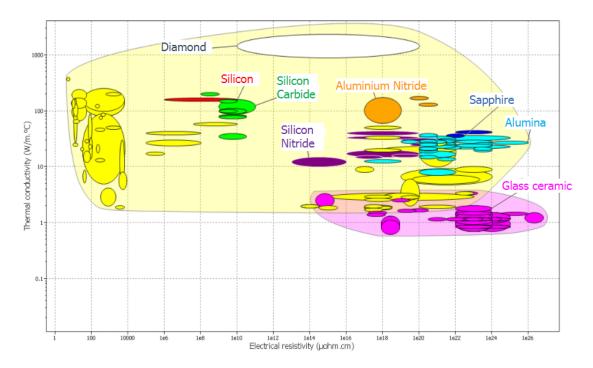

| 8.5 | Non   | Silicon Engineered Substrate9                   | 3  |

|     | 8.5.1 | Non Silicon materials for RF9                   | 3  |

|     | 8.5.2 | Example 1: Indium Phosphide on Gallium Arsenide | 6  |

|     | 8.5.3 | Example 2: Piezo on Insulator9                  | 8  |

## 1 Executive Summary

How to realize "high efficiency and low power consumption" device is a technical issue which should be emphasized on throughout the 5G RF component R&D process. The power consumption should be optimized based on the deployment plan of operators and the requirements of customers. This process should involve not only RF component vendors, but also chipset vendors and device vendors.

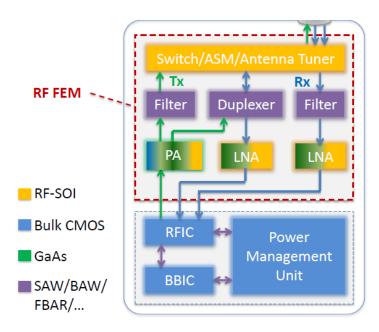

RF FEM is one of the most popular solutions to realize 5G NR RF components, especially for the large volume of high-end devices, due to its smaller layout area, better inter-stage matching, less design inputs, shorter test process and faster time to market. So FEM is a research and development direction worthy of attention.

According to 3GPP's schedule, the first version of 5G standard R15 will be completed in the middle of 2018 and R16 is going to be completed by the end of 2019. The 5G+ technical specification will be constantly updated since 2020. It is hoped that RF components vendors could actively participate in and track 3GPP's discussion on the specifications of 5G RF components as well as establish theoretical basis for the final specifications based on the prospective simulation and test data. In order to guarantee commercial RF components in time, RF components designers and manufactures should work together with operators, chipset vendors, device vendors and test instrument vendors to make sure the system verification and the pre-commercial trial could be completed in 2018 and 2019 separately The high performance and low cost front-end RF components are expected to be provided in proper time and volume. So the RF component vendors are supposed to cooperate with the whole industrial chain to accomplish the goal of 5G's commercialization by the end of 2020.

GTI 5G Device Component Research Report is expected to help people to develop 5G devices and to promote industrial development. This report may also help people to know more about the industrial status of 5G device RF components. Meanwhile, it may also help readers interested in 5G device RF components to gain from the further thinking.

## 2 Abbreviations

| Abbreviation | Explanation                                       |  |

|--------------|---------------------------------------------------|--|

| BAW          | bulk acoustic wave                                |  |

| сс           | Component Carrier                                 |  |

| CMOS         | Complementary Metal Oxide Semiconductor           |  |

| DC           | Dual Connectivity                                 |  |

| eMBB         | Enhanced Mobile Broadband                         |  |

| ESD          | Electro-Static discharge                          |  |

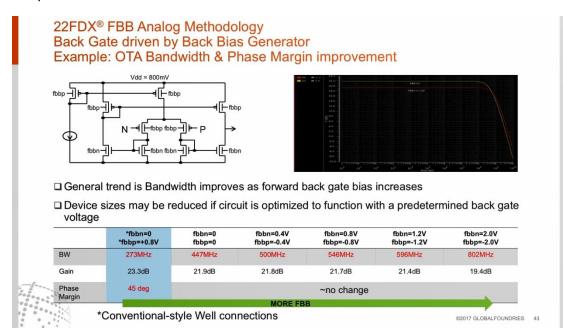

| FBB          | Forward Back Gate bias                            |  |

| FBAR         | Film Bulk Acoustic Resonator                      |  |

| FD           | Fully Depleted                                    |  |

| gNB          | NR node                                           |  |

| HEMT         | High Electron Mobility Transistor                 |  |

| HSP          | Harmonic Suppression Process                      |  |

| HPUE         | High Power UE                                     |  |

| IPD          | Integrated Product Development                    |  |

| LTCC         | Low Temperature Co-fired Ceramic                  |  |

| MEMS         | Micro-Electro-Mechanical System                   |  |

| MIMO         | Multiple-Input Multiple-Output                    |  |

| mMTC         | Massive Machine Type Communication                |  |

| mmWave       | Millimeter Wave                                   |  |

| МММВ         | Multimode Multiband                               |  |

| MMIC         | Monolithic Microwave Integrated Circuit           |  |

| MOSFET       | Metal–Oxide–Semiconductor Field-Effect Transistor |  |

| MU-MIMO      | Multi-User MIMO                                   |  |

| NSA          | Non-Standalone                                    |  |

| OFDM         | Orthogonal Frequency Division Multiplexing        |  |

| pHEMT        | Pseudomorphic HEMT                                |  |

| РРАС         | Performance, Power, Area, and Cost                |  |

| PAE          | Power Added Efficiency                            |  |

| PD           | Partially Depleted                                |  |

| RFeSI        | RF enhanced Signal Integrity                      |  |

| RFFE         | Radio Frequency Front-end                         |  |

| SAW     | surface acoustic wave                         |  |

|---------|-----------------------------------------------|--|

| SA      | Standalone                                    |  |

| SOI     | Silicon on Insulator                          |  |

| SIMOX   | Separation by Implantation of Oxygen          |  |

| SU-MIMO | Single-User MIMO                              |  |

| UE      | User Equipment                                |  |

| URLLC   | Ultra-Reliable and Low Latency Communications |  |

| UTBB    | Ultra Thin Body and Box                       |  |

| 3GPP    | The 3rd Generation Partnership Project        |  |

# GTI

## 3 Introduction

4G has completely changed our lives. While, as the society becomes much more informative, people's requirements increase rapidly. Devices are supposed to have better performance and provide more qualified service. Thus more and more opportunities and changes are created for mobile communication. Compared with 4G, 5G would have higher experiencing speed, higher connection density and lower latency. Not only the connections between people and people, but also people and things, things and things would be included into 5G scope. Aiming at constructing a cross industry ecosystem and further changing people's lives, 5G sets its sights on enhanced Mobile Broad Band (eMBB), massive Machine Type Communication (mMTC) as well as Ultra Reliable and Low Latency Communication.

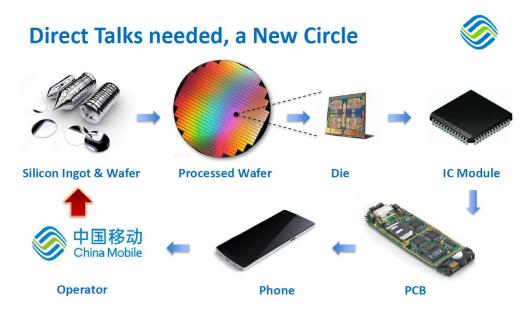

China Mobile plays an important role in prompting 5G to enter the commercial stage before 2020. As the leader of the IMT-2020 requirement group, China Mobile led to complete '5G Vision and Requirement' White Paper as well as the 5G requirements in NGMN and the 5G requirements and scenarios in 3GPP. Aiming for 5G's commercialization in 2020, sub-6GHz is the focus at this moment. Considering the millimeter Wave spectrum won't be used for mobile telecommunication until 2019 and after that 2~3 years will be needed for spectrum allocation in China, the commercialization of 5G mmWave might be 2022 or even later.

Before the commercialization in 2020, China Mobile will complete the 3-phase validation of 5G, the key technology test, the system test and the large-scale test. The key technology test has been completed in 2016, and the system test has also been completed in 2017. The large-scale test is expected to start in 2018. With the purpose of specifying the direction in developing testing prototypes, China Mobile released 'Guideline for 3.5GHz 5G System Prototype and Trial' in the early 2017 and jointly released the 'GTI Sub-6GHz 5G Device Whitepaper' in Nov. 2017 with GTI industrial partners. The guideline and the white paper analyzed the key technologies as well as the hot topics and difficult problems in the implementation of 5G pre-commercial/commercial devices. Many problems are related to 5G device RF components. So the implementation of RF components has become the key link to realize the 5G devices.

Therefore, co-operating with China Mobile 5G Innovation Center, GTI Device Working Group leads to write this "GTI 5G Device RF Component Research Report" with the industrial partners. This report mainly focuses on the 5G device RF components and has been carried out in two directions respectively, the sub-6GHz RF components and the millimeter wave RF components. Combined with the consideration of integrated circuit technology, the report analyses the industrial status, key technologies, design challenges, alternative process and research progress of core 5G RF components, such as power amplifier, filter, low noise amplifier and switch. Some related 'Black Technologies' which may have great influence on future RF components are also introduced in the report.

We sincerely thank all the contributors for their hard work in writing this report.

Chapter 5 5G Device RF Component Industry Status: HiWafer, Soitec, Qorvo, Skyworks, TAIYO YUDEN, Murata and VanChip, etc.

Chapter 6 Sub-6GHz 5G Device RF Component

6.1 Sub-6GHz 5G Power Amplifier: Skyworks, Qorvo, VanChip and HiWafer, etc.

6.2 Sub-6GHz 5G Filter: TAIYO YUDEN and Qorvo, ect.

6.3 Sub-6GHz 5G Low Noise Amplifier: Qorvo and HiWafer, etc.

Chapter 7 mmWave 5G Device RF Component: HiWafer, Murata and Qorvo, etc.

Chapter 8 Related 'Black Technologies': Soitec, Qorvo and Skyworks, etc.

Special thanks to the following contributors:

China Mobile 5G Innovation Center

#### **China Mobile Research Institute**

Dan Song, Yifan Liu, Shuai Ma, Shanpeng Xiao and Guang Yang.

#### Qorvo

Zhen Tao (Lawrence Tao)

#### Chengdu HiWafer Semiconductor Co., Ltd.

Yifeng Chen, Ting Peng, Chang Wu, Ting Fu, Xin Kong, Chunjiang Li, Yuan Zhai

#### Soitec

Bowen Lin (Stephen Lin), Eric Desbonnet and Manuel Sellier

#### Skyworks Solutions, Inc.

Yan Sun (Ryan Sun) and Kevin Walsh

#### TAIYO YUDEN CO., LTD.

Mike Tanahashi, Ryan Gu and Tao Ma

#### Murata Manufacturing Co., Ltd.

Gang Lv

#### VanChip Technologies

Gang Chen

This report will be continuously updated according to the research and development

progress.

## 4 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

[1] W-band low noise amplifier based on 70nm GaAs MHEMT process, Shaobing Wu, Weibo Wang, Fangjin Guo, Jianfeng Gao and Nianning Huang, Research and progress of SSE, April 2017.

[2] Research on InP HBT device module and circus. Rui Liu, Xi'an Electronic and Engineering University, 2014.

[3] Development and application of Inp HEMT and Inp HBT, Lihua Yao, Semiconductor technology, November 2009.

[4] Design of X-band broadband low noise amplifier MMIC, Dezhi Zhang, Jiaxiu Zhu, Jin Xu, Journal of Microwaves, October 2008.

[5] 60G high gain broadband monolithic integrated low noise amplifier, Yang Hou, Jian Zhang, Lingyun Li and Xiaowei Sun, Journal of Semiconductors, July 2008

[6] A wide-band low noise amplifier at Ka band, Haoquan Hu and Xuehui Tong, Electronic information warfare technology, July 2006.

[7] Ka-band monolithic low noise amplifier, Hao Yang, Hua Huang and Mingli Hao, Chinese journal of electron devices, August 2007.

[8] Design of general pHEMT navigation low noise amplifier, Zhichen Tu, Zhejiang University, 2016.

[9] Research progress of w-band and above MMIC amplifiers, Hewei Li, Emiconductor technology, July 2009.

[10] New developments of solid state microwave, millimeter-wave THz devices and circuits,

Zhengping Zhao, Emiconductor technology, December 2011.

[11] Embrace a brand new cooperation in 5G era, China Mobile, Danni Song, SOI consortium workshop Shanghai, September 2017

[12] RF circuit design using SOI, Leo Wilz, Skyworks, IMS 2017 short course

[13] High frequency and mm-wave Noise in SOI based CMOS: from Noise Principles to Characterizations Techniques, IEMN, Gilles Dambrine, IMS 2017 short course

[14] Benefits of 45nm Advanced Node Process for RFSOI and Applicability of a Passive Inter modulation Approach, Global Foundries, Thomas McKay, IMS 2017 short course

[15] Innovative Characterization Techniques of SOI for RF Applications, Incize, Mostafa Emam,IMS 2017 short course

[16] RF SOI from material to devices, UCL, Prof. Jean-Pierre Raskin, IMS 2017 short course

[17] SOI, from basics to applications, UCL, Cecilia Gemino, David Bold, Denis Flandres, IMS 2017 short course

[18] Engineered SOI Substrates for RF Applications, Soitec, Frédéric Allibert, IMS 2017 short course

[19] RFSOI-on-HR-Si Technologies for Wireless Reconfigurable Applications, Qorvo, Julio Costa, SOI Consortium Shanghai 2015

[20] Silicon-on-Insulator (SOI) Switches for Cellular and WLAN Front-End Applications, RFMD, Ali Tombak, IMS 2012

[21] Advanced SOI Technology for RF Applications, CEA-LETI, Christine Raynaud, SOI conference short course, 2007

[22] An Introduction to SOI Applications : Low Power to Smart Power, Soitec, Mariam Sadaka, S3S conference short course 2015

[23] 5G in Perspective - A Pragmatic Guide to What's Next, Skyworks white paper, 2017The SOI MOSFET, Tyndall National Institute, Dr Colinge, 2008

[24] Review of RF SOI Technology: a 10 years economic success story now looking toward 5G, STM, Frédéric Gianesello, S3S 2015 short course

[25] SOI overview and Assessment for Analog and Mixed-signal, UCL, Denis Flandres, SOI workshop, 2008

[26] RF SOI Device Technology Overview, UCL, Prof Raskin, S3S 2014

[27] Silicon-On-Insulator (SOI) Technology 1st Edition Manufacture and Applications, Soitec,O. Kononchuk B.-Y. Nguyen, 2014

[28] Engineering substrates new technology to accelerate 5G high frequency, Soitec, Stephen Lin, Eric Desbonnets, 5G High Frequency workshop China Mobile 2017

[29] Engineered silicon on insulator substrates and others structures to support Communication road map up to 5G, Eric Desbonnets, IWPC workshop 2016

[30] https: //www.soitec.com/en

## 5 5G Device RF Component Industry Status

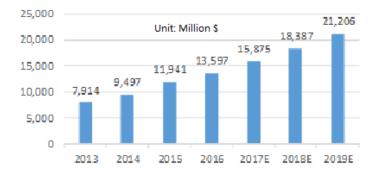

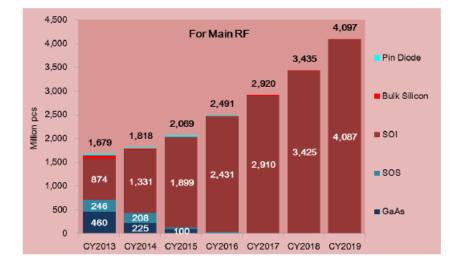

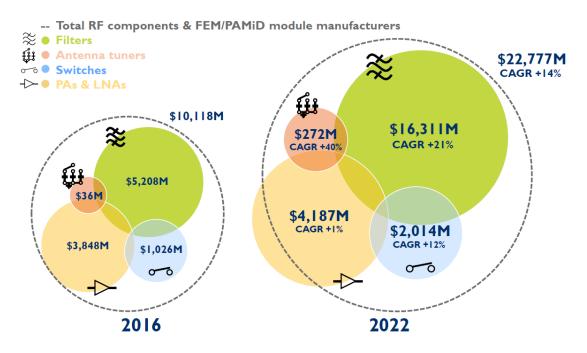

Based on the Navian predication, the total market size of RF front-end modules for mobile communications devices will grow from \$ 7.9 billion in 2013 to \$ 21.2 billion in 2019 at a CAGR of 15.4%.

Figure 5-1 Navian Predication on RF Front End Module Market

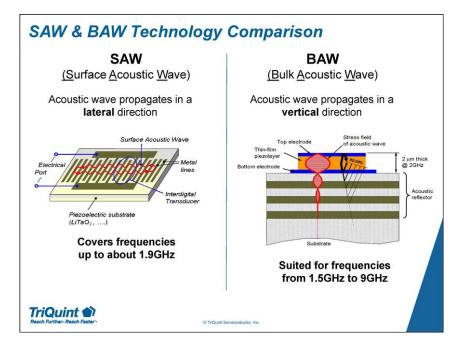

At present, the RF front-end chip market is mainly divided into two categories: a class of acoustic technology-based filters to surface acoustic wave filter (SAW) and Bulk acoustic wave (BAW) as the representative, one is the use of semiconductor technology Manufactured circuit chip, with power amplifier (PA) and switch circuit (Switch) as the representative.

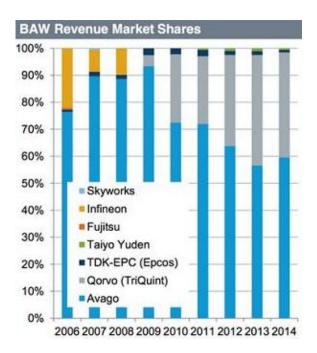

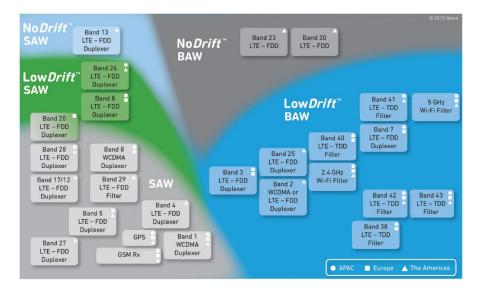

The traditional SAW filter market has become saturated, with Muruta, TDK and Taiyo Yuden accounting for more than 80% of the global market. Murata Manufacturing Co., Ltd. (Kabushiki-gaisha Murata Seisakusho) is a famous Japanese manufacturer of passive electronic components, such as capacitors and inductors, which is founded in 1940s. Ever since the beginning of the era of communications, Murata started business in RF aspects as well. After expanding the product lineup of filters, Murata achieved acquisition of Renesas Electronics and Peregrine Semiconductor, which leads to an integration of the lineup of RFFE products. Nowadays the product lineup of wireless communications department of Murata has almost covered all of the RFFE products including SAW and Multi-layer filters, RF switches, modules of either transceiver-end or receiver-end, power amplifiers, and RF connectors, etc. TAIYO YUDEN, after acquired Fujitsu Media Devices Ltd. in Y2010, has extended its technology portfolio by adding SAW and FBAR technologies in addition to LTCC RF device technology. Now the company is providing various RF devices (Filter, Duplexer, Diplexer, Low Pass Filter, etc.) for 2G/3G and 4G. While the company has already been working on the development of the series of Sub-6GHz filters for 5G since very early stages, it has also completed the initial technology validation to cover up to mmW ranges including both 28GHz and 39GHz frequency ranges in the light of upcoming 5G requirement which is being standardized within 3GPP group at this time. These three core technologies, SAW/FBAR/LTCC RF technologies, are indispensable for the implementation of upcoming 5G standard and the company will continue to enhance these technologies and develop new products through integrating three technologies. The current BAW core technologies are

mainly in the hands of Broadcom (Avago) and Qorvo, as shown in Figure 5-2. According to HIS data, Broadcom (Avago) and Qorvo have almost split their market share.

Figure 5-2 HIS Statistics on BAW Market Share (Up to 2014)

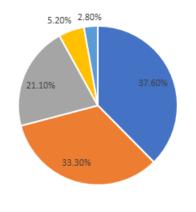

As shown in Figure 5-3, based on Navian's 2016 statistics, the device power amplifier market has an estimated \$ 13 billion market, forming the oligarchical competition between Skyworks, Qorvo and Broadcom (Avago), which together accounted for 90% % of the market share. Founded in 1962, Skyworks is an industry-leading RF front-end semiconductor solution provider that designs and manufactures radio frequency (RF) for mobile handsets, cellular network equipment, automotive, energy management, industrial and medical applications And complete semiconductor system solutions, products include amplifiers, filters, switches, attenuators, diodes, directional couplers, front-end modules. Qorvo is the new merger of RF Micro Devices and TriQuint Semiconductor, two of the industry's leading RF solutions companies. The combined Qorvo has two key product lines: the Mobile Device Product Line, the Base Station and the Military Device Product Line, both of which Line for different markets, but also in complementary areas of advanced technology research and development. Broadcom, a maker of acquisition chips for Avago Technologies, has been renamed Broadcom Limited to focus on III-V compound semiconductor design and process technology, providing a broad range of analog, mixed-signal and optoelectronic components product and system design and development. At present, major product lines include Wireless communications, cable infrastructure, enterprise storage, industrial and others.

Skyworks Qorvo Broadcom Muruta Others

Figure 5-3 Navian Statistics for the Device Power Amplifier Market (2016)

RF-device market is almost dominated by the International RF-device companies. As the developments of 4G and 5G communication networks, the domestic RF-device companies get more opportunities. Vanchip, a company running the IC design, measurement and sale business, has lots of products used in 2G/3G communications. Lansus developed domestic PA and RF switch in 2010. Its NZ5081 PA has been used in Yulong Coopad 8180 TD-SCDMA, which is the first PA used in domestic smart phone. The customer of Lansus includes Mi, Coolpad, ZTE and MEIZU. Hunstersun, a domestic 2G/3G/4G RF front end IC supplier, 600 millions sales in 2015. Products involved 3-mode-8-frequency, 5-mode-17-frequency, 2G CMOS and 3G CMOS TxM RF front end ICs. So, the domestic RF IC companies have strong ability of product developing.

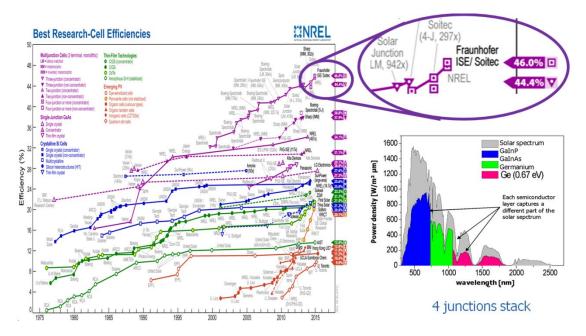

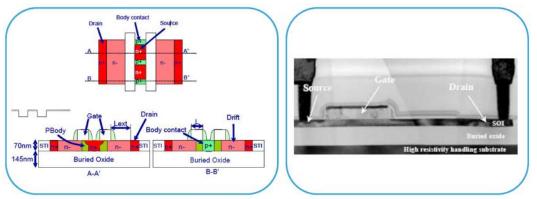

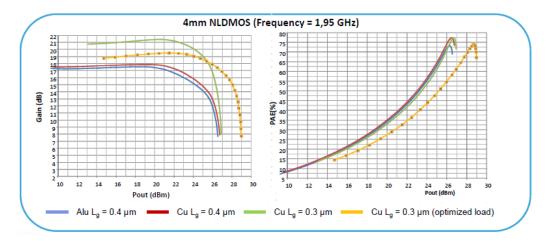

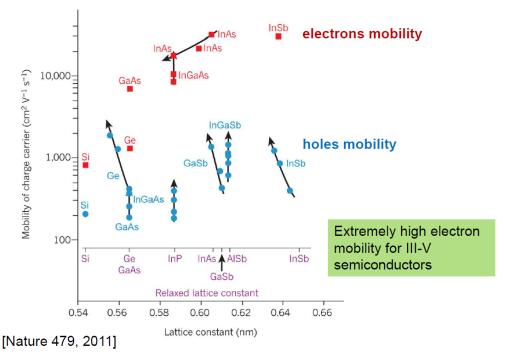

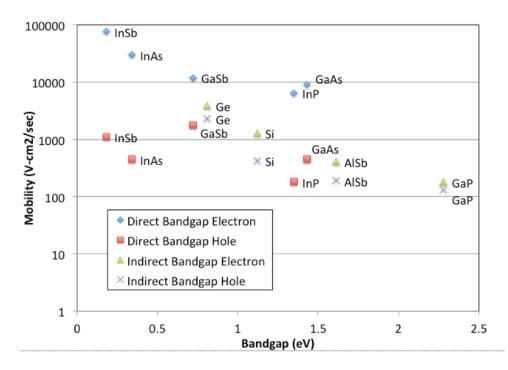

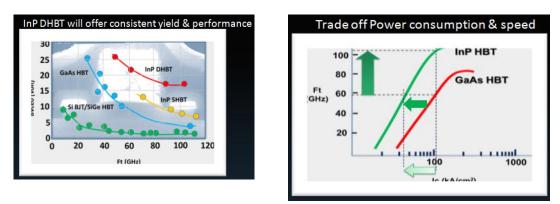

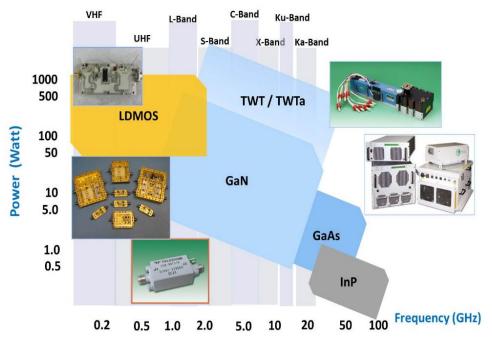

RFIC manufacturing industry is accelerating while the RFIC design houses are blooming. In the sub-6GHz band of 5G, HiWafer has developed 2um GaAs HBT process. As the mainstream technology, this process realized the monolithic integrations of the active and passive devices, which can provide better linearity, stability and reliability, This process also fits for the 3G/4G cellphone, Wifi/WiMAX, used as power amplifiers. The high frequency bands of 5G communications are near the 30GHz, 40GHz, 70GHz and 80GHz, which is a hard work for industry. HiWafer developed 0.15um GaAs pHEMT/ED HEMT process for high frequency bands of 5G. This process will support 20-60 GHz, which can be used for the high-speed data transmission in small base station, user end, IOT. With the advantages of high breakdown voltage, high electron saturation velocity and channel carrier mobility, low cost, the InP HBT and GaAs mHEMT process will get more attention.

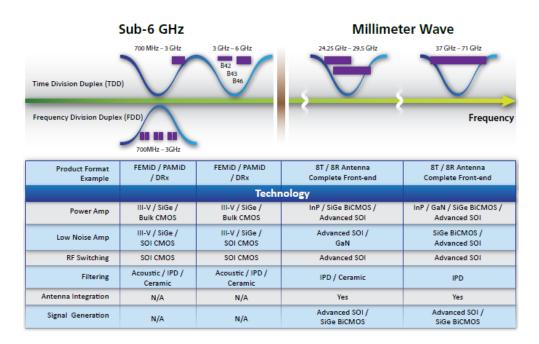

Manufacturing process is developing to adapt to the demand .In sub-6GHz band, GaAs HBT is the main technology .In the Millimeter wave, that has not come to an agreement between pHEMT, CMOS or else. HBT process technology of HiWafer is aimed at sub-6GHz market and pHEMT process is aimed at 5G high-frequency bands market.

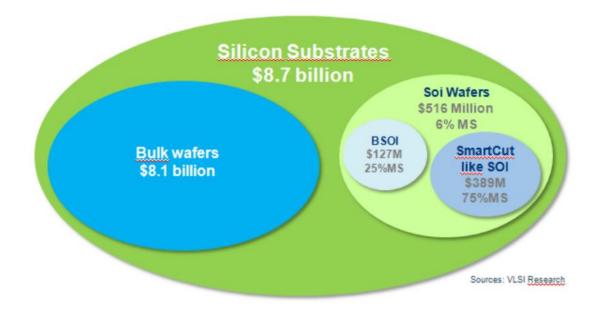

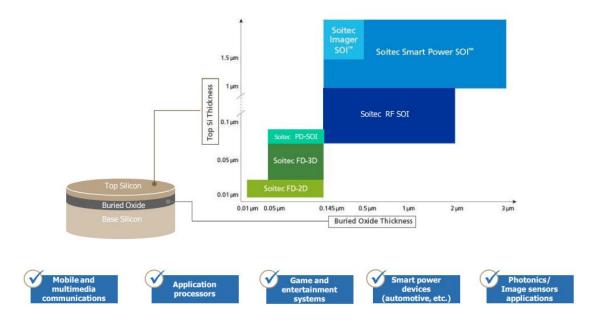

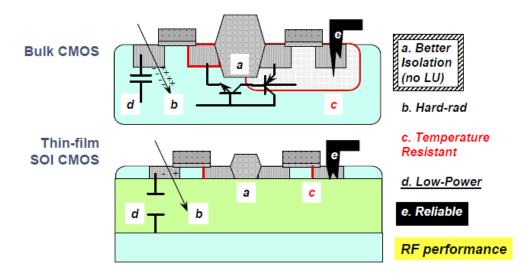

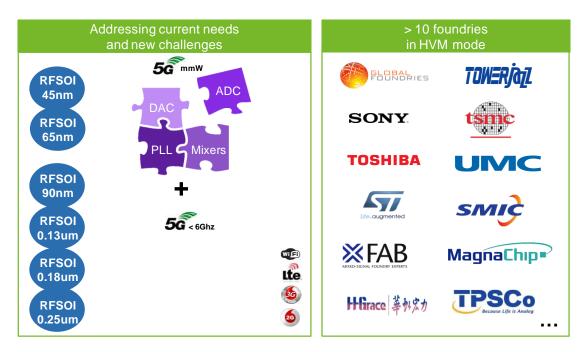

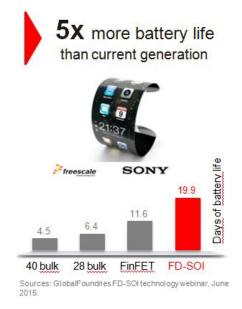

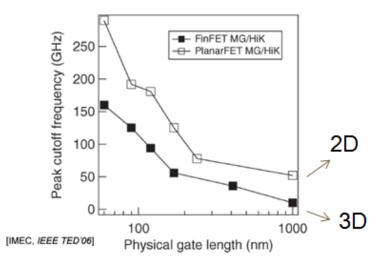

Consumers usually prefer the devices having advantages of lower price, higher efficiency, better performance and lower power consumption etc. The RF-SOI/FD-SOI technology provides possibilities for devices to realize those characteristics. Besides, SOI technology can

shorten time to market and require small design modification with low cost. With the advantages mentioned above, SOI technology has attracted more and more attentions in semiconductor industry.

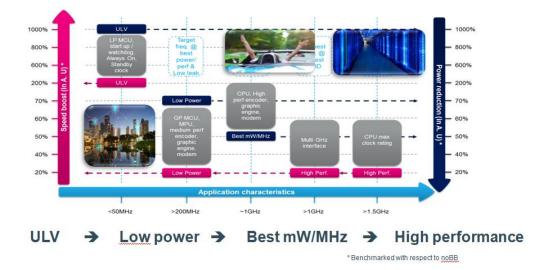

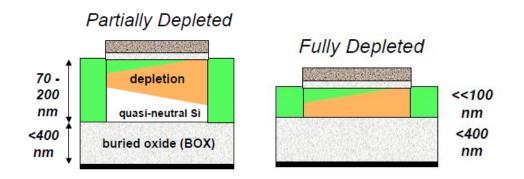

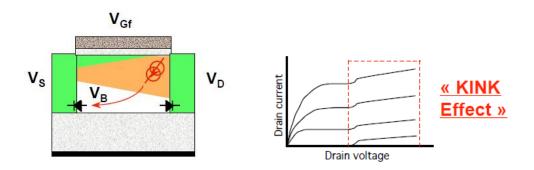

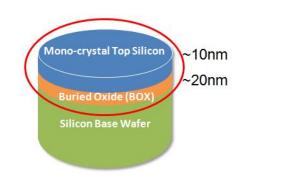

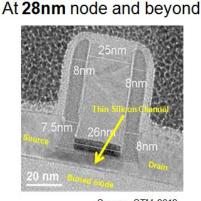

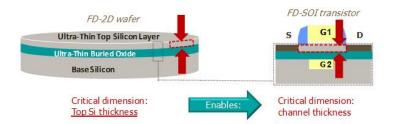

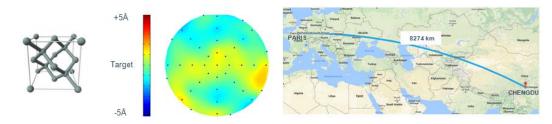

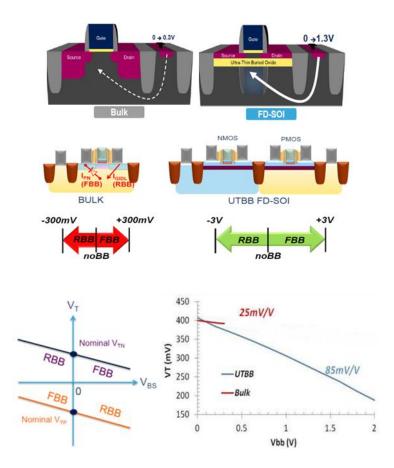

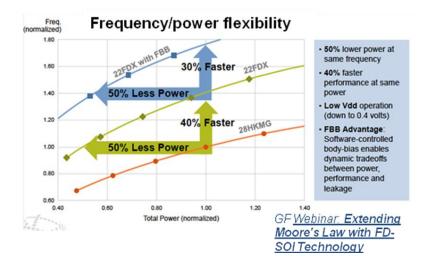

RF-SOI/FD-SOI is a kind of technology which realizing fully depleted CMOS devices on silicon on insulator (SOI). It is the only technology that combines the flat structure of 2D CMOS transistors with the fully depleted mode. SOI is one of the excellent technologies which have the good Power-Performance-Area-Cost (PPAC). It uses a kind of unique substrate material whose thickness is controlled to atomic scale and could provide excellent transistor performance. The FD-SOI technology can work on mmW band. Thus it is applied to more and more practical mmW applications, such as the entry-level processor for smart phones, System-On-Chip (SoC) for autopilot and IoT devices and radar system for 5G transceiver and automotive electronics.

Being capable of operating under extremely low power supply, the RF-SOI/FD-SOI technology gains more and more attentions for embedded applications. Thanks to adopting RF CMOS technology, FD-SOI enables single-chip solutions to be applied to more fields. This unique advantage has enabled FD-SOI to enter entry-level market, such as the function-integrated low-end smart phones and 5G mmW transceivers.

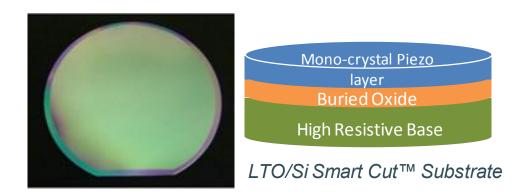

As a semiconductor materials vendor, Soitec designs and manufactures engineered substrates that are then patterned and cut into chips to make circuits for electronic components. In meeting the technical and economic challenges of mainstream electronics, SOI is helping to speed up the mobile and digital revolutions as below:

- FD-SOI and PD-SOI: for Processors & connectivity SoCs up to mmW;

- RF-SOI and POI: for RF Front-end Modules;

- Photonics-SOI: for Optical Transceivers;

- Power-SOI: for Smart Power ICs;

- Imager-SOI: for Imagers

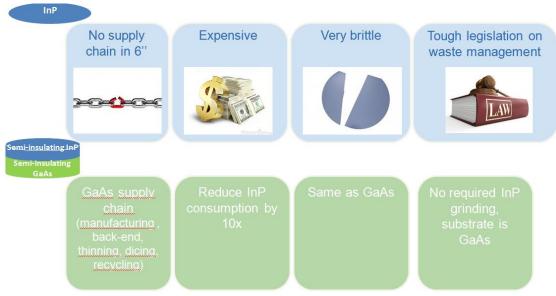

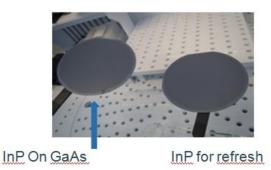

In Front End Module, substrate is the foundation of each key device. In the following report, silicon (RF-SOI, PD-SOI, FD-SOI) and non silicon (POI, InPOGaAs, etc...) engineering substrate technologies to address 5G challenges are presented.

## 6 Sub-6GHz 5G Device RF Component

## 6.1 Sub-6GHz 5G Power Amplifier

Frequency and power is the basic requirement in PA design, also Linearity, along with efficiency and bandwidth, belongs to the fundamental specification of PA design in communication systems. In a sense, efficiency and linearity are contradictory, higher

efficiency may lead to worse linearity. These two parties need to be balanced during PA design.

#### 6.1.1 Existing Mobile Device Commercial Power Amplifier

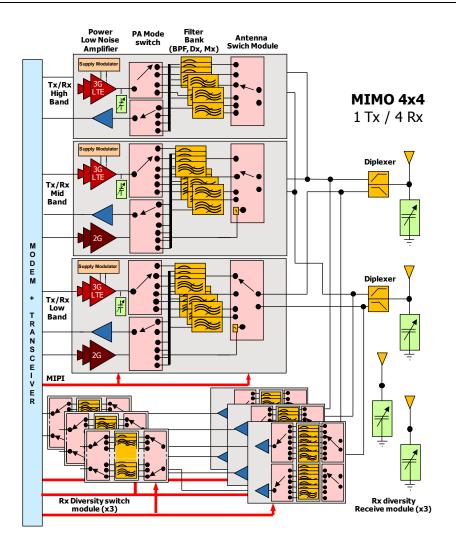

#### 6.1.1.1 Common Mobile Device RF Front-end Architecture

In commercial UE nowadays, PA needs to support 2G/3G/4G. Based on platform requirements, there are difference between 2G linear PA and 2G saturated PA(GSM saturated, EDGE linear) respectively.

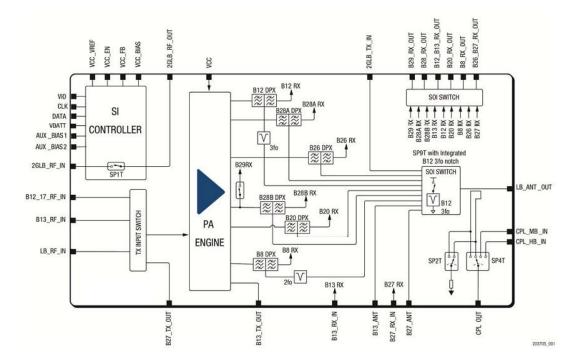

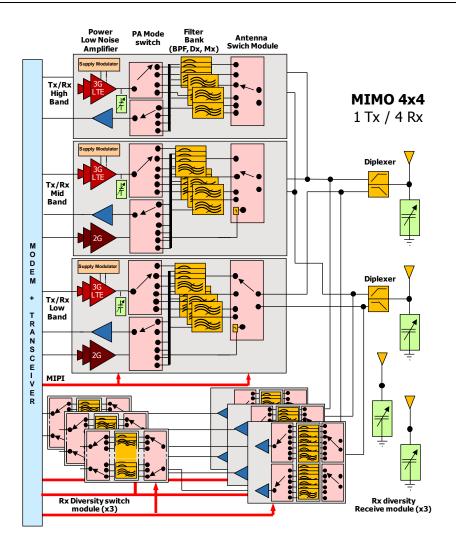

In terms of RFFE architecture, usually we can see three mainstream architectures: PAMiD architecture, MMMB PA+ASM architecture, and MMPA + TxFEM architecture. Among them, the flagship models that support most of worldwide frequency bands mainly adopt the PAMiD architecture. As shown in figure 6-1, it is block diagram of a commercial low band PAMiD, integrates all RF and analog content between the transceiver and antenna, reduce complexity, size and time-to-market for customers with demanding architectures for advanced mobile applications.

Figure 6-1 Block diagram of a commercial LB PAMiD

As shown in figure 6-2, this is block diagram of a commercial MMMB PA. The MMMB PA integrates 2G/3G/4G PA, connect with the antenna switch module ASM through external filters and duplexers. There are also some products that integrate filters and diplexer into ASM and formed the so-called FEMiD.

Figure 6-2 Block diagram of a commercial MMMB PA

MMPA+ TxFEM is the most common RF front end architecture especially in the China market. As shown in figure 6-3, MMPA only integrates 3G/4G PA. 2G PA is integrated with ASM, which is called "TxFEM".

Figure 6-3 Block diagram of a commercial MMPA and TxFEM

PS: all the figures above are provided by Skyworks

#### 6.1.1.2 Key Parameters

#### 1) Pout and Gain

The output power required by different systems is not the same. In the LTE UE, there are also different power classes like PC2 (antenna port 26dBm), PC3 (antenna port 23dBm). In order to obtain the output power of this range, the gain of the amplifier is about 20-30dB according to the level of the input signal.

#### 2) Efficiency and PAE

PA converts the DC power from power supply to AC signal power, during the conversion, part of the DC power is converted to useful signal, and the rest is consumed by the PA itself and the parasitic components in the circuit. If use PL to represent the power on the load, PD represents the DC power provided by the power supply; then the efficiency of the PA can be simply defined as PL/PD. But this does not fully reflect the amplification function of PA. Therefore, PAE is introduced to fully reflect the relationship between PA output power and power supply, which is (PL-Pin) /PD.

#### 3) Linearity

The nonlinear distortion produced by PA is reflected on both amplitude and phase. Generally, we evaluate the spectrum expansion by measuring the response of PA to the modulation signal, for example, the Adjacent Channel Leakage Ratio (ACLR).

Due to nonlinear distortion, both amplitude and phase of signal will be distorted at the same time. Therefore, we use the error between the point of the actual signal and the point of the ideal signal to represent the linearity index, which is the Error Vector Magnitude (EVM).

#### 6.1.1.3 Influence Factors

#### 1) Bandwidth and signal bandwidth

The 3.3-4.2 GHz frequency of 5G NR Band n77 has a total bandwidth of 900MHz, and it is challenging to cover such a wide band with a single PA.

Signal bandwidth is also one of the factors affecting the linearity of PA. The distortion component of the nonlinear characteristic of PA is not constant. For example, the amplitude and phase of the three or five order intermodulation will change with the amplitude and bandwidth of the input signal. This distortion component depends on the amplitude and bandwidth of the input signal, which is often called the memory effect of the power amplifier, which affects the linearity of the PA.

In the LTE system, the signal bandwidth of a single carrier is 20MHz, and in consideration of CA, it can be extended to 2CC 40MHz or even the potential 3CC 60MHz. But in 5GNR, the signal bandwidth will be greatly improved, and the linear deterioration caused by the memory effect will be a key factor in the design. NSA operation of 5G NR also calls for concurrent UL in LTE and NR which further stresses the linearity requirement.

#### 2) PAPR (peak-to-average power ratio)

PAPR is the ratio of peak power to average power. The peak power is the instantaneous peak power that occurs at a certain probability, usually 0.01% of this probability.

Because of the instantaneous high power of the signal, in order to guarantee the linear index at the instantaneous high power level, the power back off is usually used to guarantee the

linearity, and it's related with the PAPR.

The PAPR of the input signal is related to waveform and modulation, from LTE to 5G NR, the UE uplink waveform from single carrier to multi carrier. Considering the higher order modulation, 5G NR PAPR compared to LTE will be significantly increased.

3) Cooling capacity

With the increase of temperature, PA performance including gain, Pout and PAE will degrade in the device product layout, some devices close to PA will deteriorate as the working temperature increases.

HPUE (High Power User Equipment) application need to increase UE Pout from 23dBm to 26dBm, which means the heat generated from PA will also be double if we assume the PAE does not change. Also the smaller PA package size will increase the difficulty of thermal dissipation of PA. When designing PA, it is necessary to improve the heat dissipation ability of PA and reduce the working temperature of PA by reasonable and correct layout, adopting the appropriate PA structure, chip technology and packaging technology.

4) Cost

5G NR Band n77 has total bandwidth of 900MHz, also the PAPR of 5G NR signal is significantly higher than the LTE signal, these challenges will lead to different architectures. Take PA as example, use a single PA single power supply structure, adopts multi PA multi power architecture; bring in ET technology, adding DPD in PA pathway.

The PA performance of different design methods will be different, and the cost of PA will vary greatly. In the process of introducing PA products into the 5G market, excellent product performance and reasonable product cost can make the product get better market recognition.

#### 6.1.2 Sub-6GHz 5G Power Amplifier Design

#### 6.1.2.1 3GPP Standard

1) Frequency band

There have been many proposals in 3GPP, with the most emphasis placed on 3300 to 3800 MHz as a primary target with an extension to 4200 MHz to support Japan region. Current 5G NR global major band requirements are shown in figure 6-4.

|        | Ne               | w                 | E    | xisting           |       |     | Total |       |                   |       |      | Total |

|--------|------------------|-------------------|------|-------------------|-------|-----|-------|-------|-------------------|-------|------|-------|

| Region | F <sub>LOW</sub> | F <sub>HIGH</sub> | FLOW | F <sub>HIGH</sub> | Band  | BW  | BW    |       | F <sub>HIGH</sub> | Band  | BW   | BW    |

| Korea  | 3400             | 3700              |      |                   |       | 300 | 300   |       | 26.50             | 29.50 | 3.00 | 3.00  |

|        |                  |                   | 2570 | 2620              | 38    | 50  | 450   |       | 24.25             | 27.35 | 3.10 |       |

| EU     | 3400             | 3800              | 3400 | 3800              | 42+43 | 400 | 450   |       | 31.80             | 33.40 | 1.60 | 7.70  |

|        |                  |                   | 2496 | 2690              | 41    | 194 |       |       | 40.50             | 43.50 | 3.00 |       |

| Japan  | 3600             | 4200              | 3400 | 3600              | 42    | 800 | 1494  |       | 27.50             | 29.50 | 2.00 | 2.00  |

|        | 4400             | 4900              |      |                   |       | 500 |       |       | 27.50             | 28.35 | 0.85 |       |

|        |                  |                   | 2496 | 2690              | 41    | 194 |       |       | 37.00             | 38.60 | 1.60 |       |

| U.S.   |                  |                   | 3550 | 3700              | 48    | 150 | 344   |       | 38.60             | 40.00 | 1.40 | 10.85 |

|        |                  |                   | 2300 | 2400              | 40    | 100 |       |       | 64.00             | 71.00 | 7.00 |       |

|        |                  |                   | 2555 | 2655              | 41B   | 100 |       |       |                   |       |      |       |

| China  | 3300             | 3600              | 3400 | 3600              | 42    | 300 | 790   | 1.1.1 |                   |       |      |       |

|        | 4400             | 4500              |      |                   |       | 100 |       |       |                   |       |      |       |

|        | 4800             | 4990              |      |                   |       | 190 |       |       |                   |       |      |       |

Figure 6-4 Current 5G NR global major band requirements

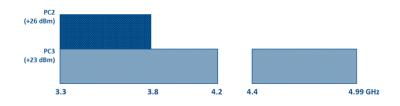

#### 2) Power level

As is in the case for TDD LTE spectrum, we anticipate power class 2 and 3 to be deployed in early 5G systems.

Figure 6-5 Power classes of 5G NR device

3) Signal Bandwidth

In terms of other rough parameters for the sub 6 GHz RF front end, we see consensus building around a maximum channel bandwidth 100MHz.

4) Waveform and modulation

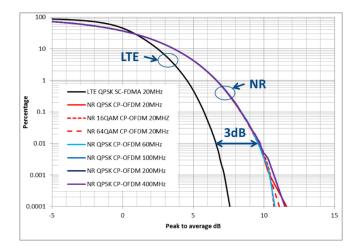

The peak to average ratio of the 5G NR signal is 3dB higher than an equivalent LTE waveform. From that we can expect impact to take the form of higher back off or higher average transmit powers. Another interesting observation is that for 5G CP-OFDM using different modulation, there is no significant difference in the CCDF function- meaning higher-order modulation has minimal impact on MPR and power back-off.

Figure 6-6 CCDF curves of CP-OFDF and SC-FDMA

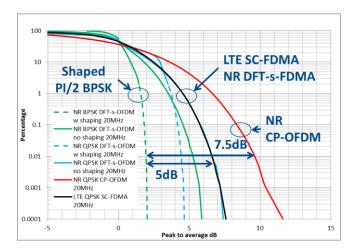

In figure 6-7 we can find CCDF curves of some lower PAPR options, which can be used in cell edge areas as well as mmWave.

Some observations on lower PAPR aspects:

- DFT-s-OFDM QPSK waveform in UL , exhibits very similar PAPR as the existing LTE SC-FDMA used in UL

- shaped PI/2 BPSK is used for sub-6GHz , also assumed for mm-Waves and provides up to 7.5dB relief

Figure 6-7 CCDF curves of some alternate candidate waveforms.

#### 6.1.2.2 Design Challenges

#### 1) RF path Co-banding

The frequency below 6GHz is still scarce resources. There may be LTE and 5G NR working on the same frequency band. Different operators will make different deployment between LTE and 5G NR.

As shown in table 6-1, it is possible for LTE to share the same RF path with 5G NR on UE. The

co-path can not only save the hardware cost of the RF front-end devices, but also reduce the PCB area. Of course, this also requires LTE and 5G NR be fully aligned on the time slot, otherwise the coexisting interference problem will be caused.

| LTE Band number | UL           | DL           | Duplex mode |

|-----------------|--------------|--------------|-------------|

| B42             | 3.4-3.6 GHz  | 3.4-3.6 GHz  | TDD         |

| B43             | 3.6-3.8 GHz  | 3.6-3.8 GHz  | TDD         |

| B48             | 3.55-3.7 GHz | 3.55-3.7 GHz | TDD         |

| NR Band number  | UL           | DL           | Duplex mode |

| n77             | 3.3-4.2 GHz  | 3.3-4.2 GHz  | TDD         |

| n78             | 3.3-3.8 GHz  | 3.3-3.8 GHz  | TDD         |

There are have many challenges to achieve LTE and NR co-path, not only because the signal bandwidth of NR is much more than that of LTE, but also because NR needs to support PC2, and the peak to average ratio is higher, which leads to slight degradation of efficiency under LTE. At the same time, the coexistence requirement will also require the device to guarantee the intra-band RF performance defined by 3GPP.

2) Interference in UE

Except the case that NR operation with only one UL band under SA mode, UE may suffer from in-device interference due to simultaneous UL transmissions in the NSA deployment and SUL under SA deployment.

There are three different types of in-device interference due to simultaneous UL transmission over different bands:

• Interference from Intermodulation (IMD)

This kind of interference comes from the intermodulation (IMD) product between lower-frequency and higher-frequency UL carriers, which may fall into the DL carrier. One example is that when a UE is transmitting simultaneously on B3 (LTE) and NR sub-6G band (3.3G~4.2G), interference of IM2/IM4/IM5 will fall into B1 LTE receiver.

• Interference from Harmonic

This kind of interference comes from the harmonic of lower- frequency UL signals to the higher- frequency DL signals when the harmonic of UL frequency falls into the DL frequency. One example is that when a UE is simultaneously transmitting on B3 (LTE) and receiving on NR sub-6G band B42 (3.4G~3.6G), interference from H2 of B3 will fall into NR receiver.

• Interference from Harmonic mixing

This kind of interference comes from higher frequency UL signals to the lower- frequency DL signals when the higher frequency is multiple of the lower frequency. One example is that when a UE is simultaneously transmitting on NR 3.3GHz~4.2GHz and receiving on LTE B26, interference from NR UL will fall into LTE B26 receiver and be demoded by receiver which

causes sensitivity degradation.

3) Thermal Distribution

PA (Power amplifier) performance will degrade as temperature rises due to its device properties. Specifically, the higher the temperature, the lower its Gain, Output Power and Power Added Efficiency. In the end user equipment, some components such as Duplexers that are physically in adjacent with PA will experience performance degradation too. With the requirement of HPUE(High Power User Equipment) on devices, the output power at antenna will be increased from 23dBm to 26dBm, which means heat generated from PA will double assuming PA maintains same power added efficiency. In addition, a smaller footprint of PA makes heat dissipation even worse.

As a consequence, when designing a PA, one needs to take into account the architecture, process and assembly to improve the PA thermal distribution.

4) Cost

5G NR band 77 has large bandwidth (3.3-4.2GHz). Its signal has higher PAR (Peak to Average Ratio) than that in LTE. Furthermore, different frequency bands inside 3.3GHz-4.2GHz have different output power requirements. These challenges call for different PA architectures, for example, single PA with single supply, or multiple PA paths with multiple supplies, EER (Envelop Elimination and Restoration) with traditional supplies or ET (Envelop Tracking) , DPT(Digital Pre-Distortion) in the PA signal path, etc.. All these factors will impact PA cost and performance, a good balance of which will help the acceptance by the marketplace of such 5G PAs.

#### 6.1.2.3 Alternative Processes

There are only two foundries in China can provide the GaAs pHEMT process now, one is Hiwafer in Chengdu, the other is Sanan in Xiamen.

6-inch 2um GaAs HBT process named as HBT02, can be used in high-frequency, high-linearity PA applied in cell phone, WiFi, Pad and other. This process is fit for sub-10GHz region: 4G LTE, 3G/2G, WiFi and base station. And provides two kinds of HBT, one is high  $\beta$  version, the other is low  $\beta$  version.

The BiHEMT process of HiWafer, which can be used to produce logic module and RF module simultaneous, is now under research. The development of BiHEMT process can increase the IC functional complexity and integration density.

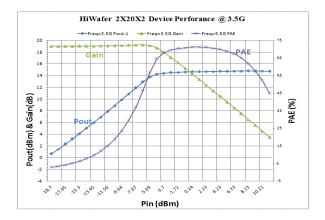

The performances and measurement results of 6-inch 2um GaAs HBT process are given in table 6-2 and figure 6-8:

| Darametro | HiWafer |

|-----------|---------|

| Parametre | HBT02   |

#### Table 6-2 Performances of 6-inch 2um GaAs HBT process

GTI 5G Device RF Component Research Report

| Beta(V)                         | 120 (@1kA/cm <sup>2</sup> ) | 75(@1kA/cm <sup>2</sup> )  |

|---------------------------------|-----------------------------|----------------------------|

| BVcbo(V)                        | 24 (@2kA/cm <sup>2</sup> )  | 24 (@2kA/cm <sup>2</sup> ) |

| BVceo(V)                        | 13 (@2kA/cm <sup>2</sup> )  | 13 (@2kA/cm <sup>2</sup> ) |

| ft/fmax(GHz)                    | 40/60                       | 40/60                      |

| ResistorTaN $(\Omega/\Box)$     | 50                          | 50                         |

| Capacitor (pF/mm <sup>2</sup> ) | 600/930                     | 600/930                    |

| Au: M1/M2(μm)                   | 1/2                         | 1/2                        |

The key parameters in table 6-2 are explained as follows:

- Beta(β): current gain, the 75-Gian transistor is commonly used in 3G, the 120-Gain transistor is commonly used in 4G and the later generations.

- BVcbo, BVceo: the breakdown voltage, the higher breakdown voltage means higher work voltage.

- ft: current cut-off frequency. The higher the ft, the better frequency characteristics.

- fmax: highest oscillation frequency, where the power gain of the transistor decreases to 1.

Figure 6-8 Measurement results of 6-inch 2um GaAs HBT process

GaAs device have the advantages of high electron mobility, low loss semi-insulating substrate, high linearity, high cut-off frequency, and high breakdown voltage, making them superior to CMOS in power performance. Therefore, GaAs device holds a dominant position in performance advantages over CMOS in the 4G PA market. For the future 5G PA market, the standard GaAs based modules will continue to maintain their advantages in power performance. In the whole market, compared with the highly integrated CMOS device and high power performance GaN device, GaAs device can continue to play its performance advantages by increasing its level of integration through processing and packaging.

Considering the fact that GaAs and silicon-based devices are still able to meet the cost and performance requirements. GaN device will not be used in 4G mobile phones for its still high working voltage. However, with the development of GaN technology, GaN device may be used in 5G mobile phone RF front-end module. Compared with high frequency devices such

as GaAs and InP, the power density of GaN devices will be greater, which will help reducing the chip area of the PA. Compared with LDCMOS and SiC, GaN has better frequency characteristics; GaN device also has wider the instantaneous bandwidth, thus fewer amplifiers are needed to cover all bands and channels. GaN device has many other advantages, such as higher output impedance. High output impedance makes it easier for impedance matching and power combining of GaN device, and to cover a wider frequency range and improve the applicability of RF power amplifiers.

GaN applied in 5G phones, there are several problems need to be solved:

- GaN devices work in low voltage.

- The high thermal conductivity in cell phone

- High cost

#### 6.1.2.4 Existing Sub-6GHz 5G Power Amplifier Products

1. Measured Data of Sub-6GHz 5G NR PA

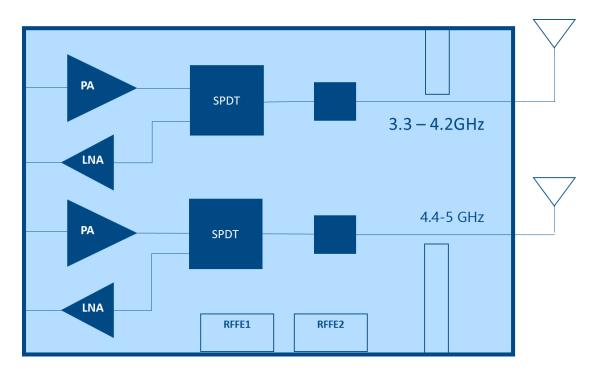

Currently, the RF front-end module that supports 3.3GHz-4.2GHz and 4.4GHz-5GHz for 5G NR 3GPP standards is under develop, and a conceptual image of the fully technology demonstrator for sub 6 GHz TDD systems in 3.5/4.5 GHz could look like this. Actual Implementation is likely to vary, but the main concepts remain intact.

Figure 6-9 Block diagram of RFFE module support 3.3GHz-4.2GHzand 4.4GHz-5GHz

The PA in the sub-6 GHz module will be assumed to be LTE and 5G NR compatible. The PA will have to be designed to support power class 2 HPUE in at least some sections of the band. In general, Support for:

#Res BW 220 kHz

Sweep Time 267 ms (1001 pts)

- LTE and 5GNR PC 3 and PC 2

- CP-OFDM and DFT-s-OFDM waveforms

- Full and Partial allocations (at channel edge and in-channel)

- 20MHz and 100MHz bandwidths

- QPSK, 16QAM and 64QAM

- Normal, clipped or low PAPR waveforms

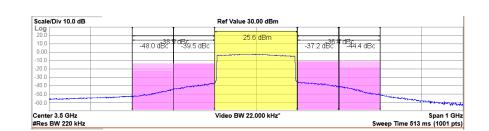

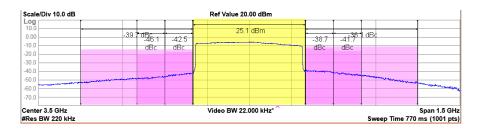

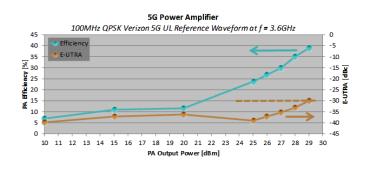

As shown in figure 6-10, we use CP-OFDM QPSK Full RB waveform and 3.8V power supply, PA Engine can achieve 26.9dBm@100MHz for -36dBc ACLR, almost same power capability is maintained for 200MHz 400MHz channel bandwidths. and Scale/Div 10.0 dB Ref Value 20.00 dBm 26.0 dBm 0.00 -37 6 dBc -36.3 dBc -52.8 dBc -53.3 dBc -20.0 -30.0 -40.0 -50.0 -60.0 70.0 Cent 3.5 GHz o BW 22.000 kHz Span 519.6

In figure 6-11, shows the corresponding changes of linearity and efficiency

Figure 6-11 Efficiency and ACLR test results based on MP PA engine

PS: all the figures above are provided by Skyworks.

#### 2. Measured Data of Sub-6GHz 5G NR PA

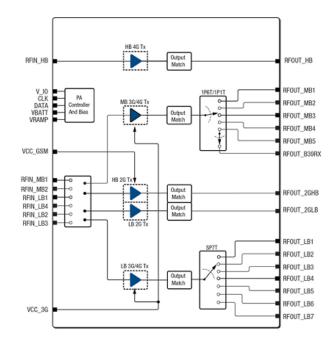

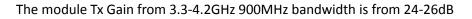

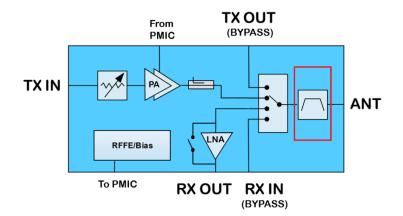

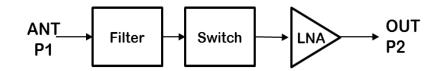

Now according to 5G NR Standalone 3GPP specification, supporting Band n77 3.3GHz-4.2GHz 900MHz bandwidth RF front end module is already developed. The block diagram is in Figure 6-12

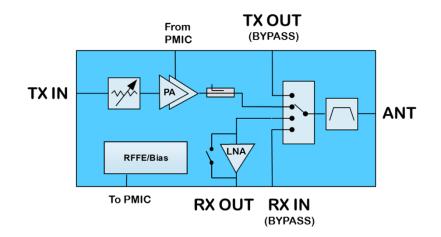

Figure 6-12 5G NR RF Front End Module Block Diagram

This RF Front End Module integrates power amplifier, Tx/Rx pass band filter, LNA, Switch and coupler.

Supporting linear output power 24.5dBm (Power Class 3) at Ant port.

- a) Supporting high PAR of ~9dB 5G CP-OFDM modulation

- b) Supporting max CA bandwidth of 400MH, 4CC

- c) Supporting QPSK/16QAM/64QAM modulation signal

- d) Supporting 2dB max power back off to 22.5dBm (single carrier 100MHz bandwidth and 64QAM modulation signal)

- e) Supporting 3dB max power back off to 21.5dBm (4CC 400MHz bandwidth and 64QAM modulation signal)

- f) Supporting APT technology

Detailed RF front end module measurement condition and data are as below:

- a) Test Condition

- Linear 22.5dBm output power at Ant port

- CP-OFDM 5GNR input waveform

- Single carrier 100MHz bandwidth

- 64QAM modulation

- 4.5V constant supply voltage

- b) Test Data

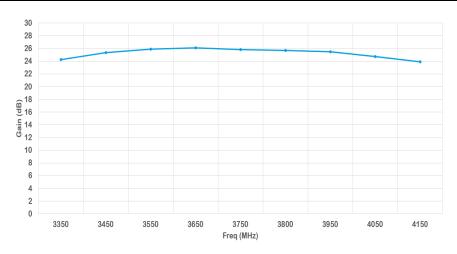

Figure 6-13 5G NR RF Module Gain data

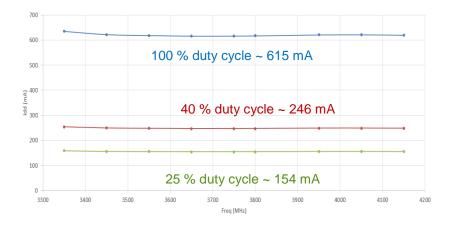

Figure 6-14 5G NR RF Module power consumption based on different duty cycles F Module ACLR within 3.3-4.2GHz is less than -36dBc.

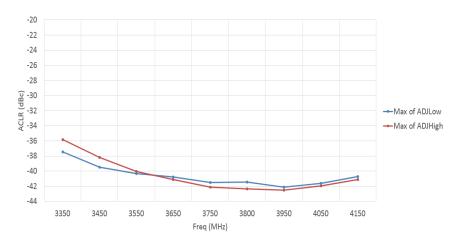

Figure 6-15 5G NR RF Module ACLR

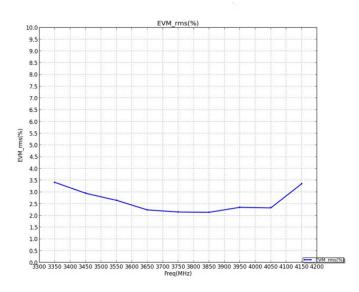

RF Module EVM within 3.3-4.2GHz is less than 3.5%.

Figure 6-16 5G NR RF Module EVM Data

Note: Above RF Module information and data are provided by Qorvo.

3. System Diagram of Sub-6GHz 5G NR PA

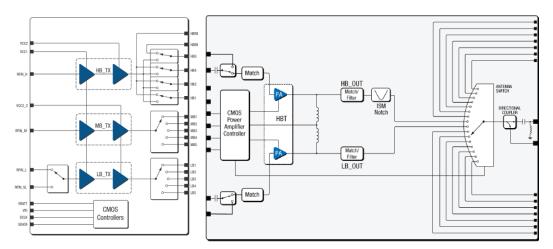

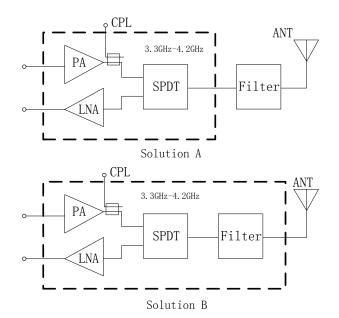

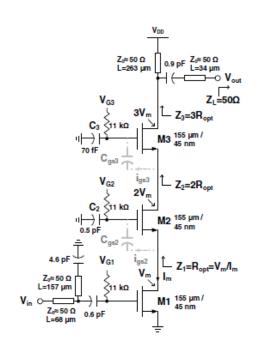

Vanchip is developing a 5G RFFEM (RF Front End Module) supporting 3.3GHz-4.2GHz. Figure 6-17 below is the system diagram.

Figure 6-17 5G NR RF Front End Module Diagram

In Solution A, a 3.3GHz-4.2GHz PA, a coupler, a LNA (low noise amplifier) and SPDT switch are integrated in a single module. Customers can place the filter on PCB to meet their requirements on performance and cost.

In Solution B, filter is placed into the module to optimize the module performance and to achieve the maximum integration for customers.

Both solutions support requirements as below:

- a) PC2, PC3 in 5G NR and LTE

- b) QPSK/16QAM/64QAM Modulation

- c) CP-OFDM and DFT-s-OFDM Waveform

- d) Maximum 400MHz 4 Carrier Aggregation

- e) APT and ET

### 6.2 Sub-6GHz 5G Filter

#### 6.2.1 Existing Mobile Device Commercial Filter

The rapid growth in mobile wireless data and 4G LTE networks has created an ever-increasing requirement for new spectrum bands to accommodate wireless traffic. Whereas 3G networks used only about five bands, there are already over 20 4G LTE bands and this number could rise to more than 40 in the near future.

Though it's not practical to support all worldwide bands in a single smartphone, a

feature-rich model for international use may need to filter transmit and receive paths for 2G, 3G, and 4G in up to 15 bands, as well as Wi-Fi, Bluetooth, and global navigation satellite system (GNSS). Such a phone may require as many as 30 to 40 filters. The situation is likely to become even more complex with next-generation high-end smartphones requiring even more filters.

#### 6.2.1.1 Common Types of Filter

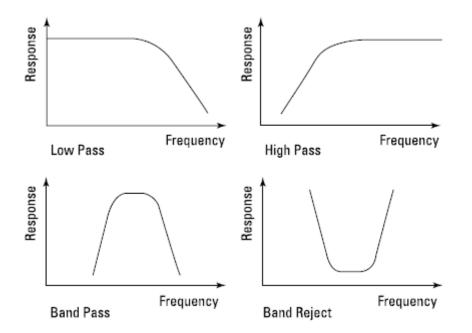

A filter removes unwanted frequency components from a signal while preserving desired frequency components. There are four basic types of filters that accept or reject signals in different ways (see Figure 6-18). The different types are defined as

- Low pass: Allows all frequencies below a certain frequency to pass while rejecting all others (opposite of high pass)

- High pass: Allows all frequencies above a certain frequency to pass while rejecting all others (opposite of low pass)

- Band pass: Allows all frequencies between two frequencies to pass while rejecting all others (opposite of band stop)

- Band stop (or band reject): Rejects all frequencies between two frequencies while passing all others (opposite of band pass)

Band stop and band reject filters are also known as notch filters.

Filter construction varies by application, with size, cost, and performance the major variables. Here are some example filter constructions:

- Discrete inductor-capacitor (LC) filters are low-cost structures of moderate performance and size. The LC elements are sometimes implemented as printed structures on substrates called an integrated passive device (IPD).

- Multilayer ceramic filters are low to moderate cost and have similar performance to LC filters. Their footprint is generally reasonable, but their thickness is becoming an issue as mobile applications emphasize thinner and thinner designs.

- Monoblock ceramic filters are much higher performance than multilayer ceramics and also more expensive. They're also physically larger and usually aren't suitable for mobile applications.

- Acoustic filters have the capability to meet both low and high frequencies up to 6 GHz, are small in size, and offer the best performance and cost for complex filter requirements. Acoustic filters are the most common filter construction for mobile devices.

- Cavity filters are used in infrastructure applications only. They can achieve good performance at reasonable cost but are large.

#### 6.2.1.2 Key Parameters and Influence Factors

Filters can be designed to meet a variety of requirements. Although they use the same basic circuit configurations, circuit values differ when the circuit is designed to meet different criteria. In-band ripple, fastest transition to the ultimate roll-off, and highest out-of-band rejection are some of the criteria that result in different circuit values. Filters allow only particular frequencies or bands of frequencies to pass through and are, thus, an essential tool for RF design engineers. Typical filter response curve is shown in Figure 6-19.

Figure 6-19 Typical Filter Response Curve

In case your knowledge of electronics is a bit rusty, here's a brief tutorial on some of the more important terms and concepts to help refresh your memory.

- 1) Attenuation: An amplitude loss, usually measured in decibels (dB), incurred by a signal after passing through an RF filter.

- 2) Cutoff: Normally taken to be the point at which the response of the filter has fallen by 3 dB.

- 3) Group delay: The derivative of a filter's phase with respect to frequency. Group delay, measured intime (in seconds), can be thought of as the propagation time delay of the envelope of an amplitude modulated signal as it passes through an RF filter.

- 4) Insertion loss: Loss of signal power resulting from the insertion of a component.

- 5) Isolation: Separation of one signal from another to prevent unintentional interaction between them (for example, transmit and receive interaction).

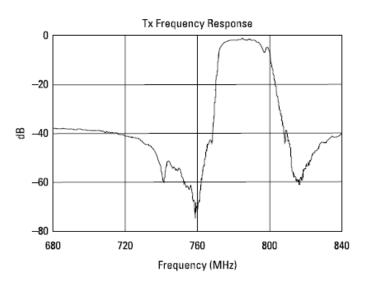

- 6) Q factor: The "quality" factor is a measure of the selectivity of a resonant circuit described as the ratio of stored versus lost energy per oscillation cycle.

- 7) Passband: The region through which the signal passes relatively unattenuated.

- 8) Ripple: The variation of insertion loss in the passband.

- 9) Selectivity: A measurement of the capability of the filter to pass or reject specific frequencies relative to the center frequency of the filter. Selectivity is usually stated as the loss through a filter that occurs at some specified difference from the center frequency of the filter.

- 10) Stopband: A band where the filter has reached its required out-ofband rejection, defined as a required number of decibels.

The figure shows some clear trends:

- 1) Loss increases as the Q factor drops and increases more rapidly for lower values of resonator Q.

- 2) The edges of the passband become more rounded and the passband narrower as the Q decreases. Note how each successively lower Q plot fits inside the previous.

- 3) The loss at the passband edges increases more than loss in the middle of the band. This poses a serious problem for modulations that go right to the edge of the passband.

Fiture 6-20 Acoustic Filter Attentuation based on different Q

Narrow modulations such as GSM (200 kHz) and CDMA (1.25 MHz) will suffer the most sensitivity loss at the band edge due to this effect, while WCDMA (3.84 MHz) will suffer less. LTE results depend on the system bandwidth, with narrower bandwidths more affected.

#### 6.2.1.3 Acoustic filter

Acoustic filter technologies continue to evolve to meet the challenges of the global transition to 4G networks. In this chapter, you find out about surface acoustic wave (SAW) and bulk acoustic wave (BAW) filter technologies, which are used to solve many of today' s toughest mobile device filtering problems.

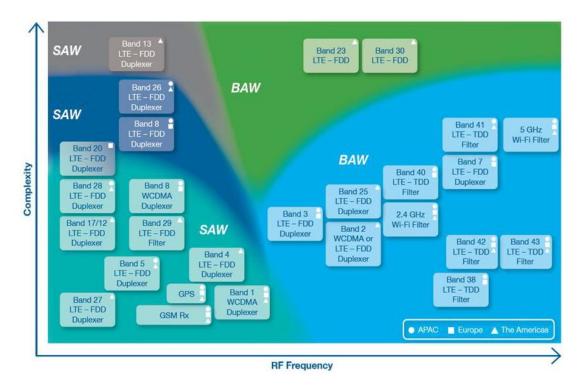

#### 1) SAW: Mature But Still Growing

SAW filters are widely used in 2G and 3G receiver front ends, duplexers, and receive filters. SAW filters combine low insertion loss with good rejection, can achieve broad bandwidths, and are a tiny fraction of the size of traditional cavity and ceramic filters.

Because SAW filters are fabricated on wafers, they can be created in large volumes at low cost. SAW technology also allows filters and duplexers for different bands to be integrated on a single chip with little or no additional fabrication steps.

The piezoelectric effect that exists in crystals with a certain symmetry is the 'motor' as well as the 'generator' in acoustic filters. When you apply a voltage to such a crystal, it will deform mechanically, converting electrical energy into mechanical energy. The opposite occurs when such a crystal is mechanically compressed or expanded. Charges form on opposite faces of the crystalline structure, causing a current to flow in the devices and/or voltage between the devices. This conversion between electrical and mechanical domains happens with extremely low energy loss, achieving exceptional efficiency inboth directions.

In solid materials, alternating mechanical deformation createsacoustic waves that travel at velocities of 3,000 to 12,000 meters per second. In acoustic filters, the waves are confined to

create standing waves with extremely high-quality (high-Q) factors of several thousand. These high-Q resonances are the basis of the frequency selectivity and low loss that acoustic filters achieve.

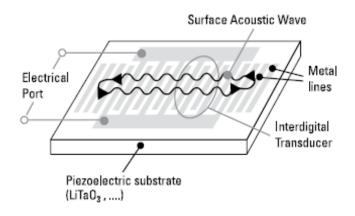

In a basic SAW filter (see Figure 6-21), an electrical input signal is converted to an acoustic wave by interleaved metal interdigital transducers (IDTs) created on a piezoelectric substrate, such as quartz, lithium tantalite (LiTaO3), or lithium niobate (LiNbO3). Its slow velocity makes it possible to fit many wavelengths across the IDTs in a very small device.

Figure 6-21 SAW Filter Architecture

A key advantage of SAW is its capability to optimally meet standard filter applications up to 1.9 GHz, including several standard bands such as GSM, CDMA, 3G, and some 4G bands.

Additionally, techniques such as wafer level packaging (discussed in Chapter 6) are being used to shrink SAW filters, allowing the integration of filters and duplexers for multiple bands onto a single chip. This is becoming increasingly important as smartphones incorporate more functions.

SAW filters, however, have limitations. Above about 1 GHz, their selectivity declines, at about 2.5 GHz.

The use of SAW is limited to applications with modest performance requirements SAW is also very temperature sensitive, this issue is better handled by temperature compensated SAW technology (TC-SAW). The stiffness of the substrate material tends to decrease at higher temperatures and acoustic velocity diminishes. A SAW filter's response may shift downward by as much as 4 MHz as temperature increases. This limitation has become more significant as guard bands become narrower and consumer devices are specified to operate across a wide temperature range (typically,  $-20^{\circ}$  C to 85° C).

### 2) BAW: High Performance

BAW filters generally deliver superior performance (higher Q) with lower insertion loss at higher frequency levels. With BAW technology, it is possible to create narrowband filters with exceptionally steep filter skirts and excellent rejection. This makes BAW the technology of choice for many challenging interference problems. BAW delivers these benefits at

frequencies above 1.5 GHz, making it a complementary technology to SAW (which is most effective at lower frequencies). BAW can address frequencies up to 6 GHz and is used for many of the new LTE bands above 1.9 GHz. BAW is also highly effective for LTE/Wi-Fi coexistence filters.

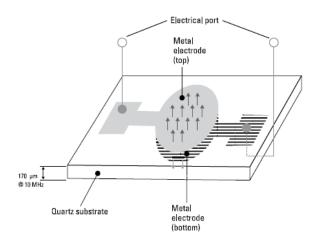

BAW filter size also decreases with higher frequencies, which makes these filters ideal for the most demanding 3G and 4G applications. In addition, BAW design is far less sensitive to temperature variation even at broad bandwidths.

Unlike SAW filters, the acoustic wave in a BAW filter propagates vertically (see Figure 6-22). In a BAW resonator using a quartz crystal as the substrate, metal patches on the top and bottom sides of the quartz excite the acoustic waves, which bounce from the top to the bottom surface to form a standing acoustic wave. The frequency at which resonance occurs is determined by the thickness of the slab and the mass of the electrodes. At the high frequencies in which BAW filters are effective, the piezo layer must be only micrometers thick, requiring the resonator structure to be made using thin-film deposition and micro-machining on a carrier substrate.

Fiture 6-22 BAW Filter Architecture

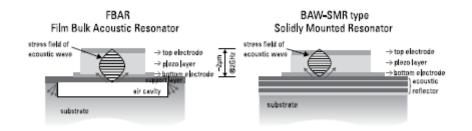

To keep the waves from escaping into the substrate, an acoustic Bragg reflector is created by stacking thin layers of alternating stiffness and density. The result of this approach is called a solidly mounted resonator BAW (BAW-SMR). A Bragg reflector is a structure formed from multiple layers of alternating materials with varying refractive index.

An alternative approach, called a film bulk acoustic resonator (FBAR), etches a cavity underneath the active area, creating suspended membranes. Figure 6-23 compares BAW-SMR and FBAR filter designs.

Figure 6-23 FBAR Vs BAW-SMR Architecture

Both types of BAW filters can achieve very low loss because the density of their acoustic energy is very high and the structures trap acoustic waves very well. Their achievable Q is higher than any other type of filter of reasonable size employed at microwave frequencies: 2,500 at 2 GHz. This results in superb rejection and insertion loss performance, even at the critical pass band edges.

The fundamental difference between FBAR and BAW-SMR is in how acoustic energy is trapped. For FBAR, the air/crystal interface on both faces of the resonator ensures that the main mode of interest is appropriately trapped. In BAW-SMR, Bragg reflectors underneath the resonator effectively trap this mode. Another major difference between FBAR and BAW-SMR is the thermal path for heat generated in the device. In BAW-SMR, the heat has a conduction path into the substrate from which it can be spread. In FBAR, because there is an air gap on each side of the resonator, the thermal conduction path is weaker.

Because BAW filters offer low insertion loss, they help compensate for the higher losses associated with the need to support many bands in a single smartphone. Besides improving signal reception, lower loss also contributes to longer battery life. BAW excels in applications where the uplink and downlink separation is minimal and when attenuation is required in tightly packed adjacent bands.

Figure 6-24 2G/3G/4G Filter Technology from Qorvo

## 6.2.2 3.3GHz-4.2GHz 5G Filter Design

### 6.2.2.1 Design Challenges

Upcoming RF architecture for 5G to be introduced in 2020 and beyond would further require higher frequency and wider frequency bandwidth as it is being standardized under 3GPP Release 15. Filtering devices would be required to cover rather much higher relative bandwidth ratio as opposed to current 4G requirement as well as the compatibilities to HPUE requirement which is considered to be standardized within Release 15 while filtering devices are expected to provide rather lower insertion loss as well as decent attenuation level. Furthermore, when initial 5G implementation is done by NSA (Non-Standalone) mode, this may possibly generate IMD issue which would require filtering devices to provide lower passive inter-modulation characteristics. Therefore, upcoming new filtering RF devices must consider satisfying these potential issues.

### 6.2.2.2 Alternative Processes

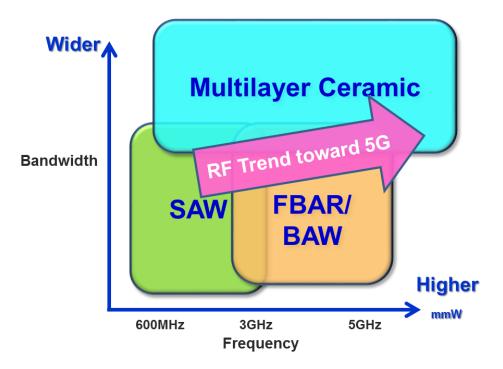

Combine with 6.2.1.3 introduction of SAW filter, as the following chart 6-25, at the present the technology of filters have been divided to 3 series: ONE is SAW technology, it has always been utilized for main bands of cellular phone standard and this should continue to be the case as 5G will be using existing LTE bands after refarming by 3GPP. But it is difficult to meet the requirement of 5G high frequency and wider frequency bandwidth; TWO is FBAR/BAW technology, it has mainly been utilized for satisfying rather stringent attenuation and somewhat higher frequency requirement especially for the solution of coexistence with

adjacent systems. This technology is capable of covering up to approximately 3800MHz ranges while the company has been working to push the envelope toward even much higher frequency ranges especially to satisfy upcoming 5G requirement. THREE is LTCC (Low Temperature Co-fired Ceramic) technology. It is capable of meeting wider frequency bandwidth and higher frequency requirement. Similar to LTCC, LC structures on IPD technology, while a bit lower Q, are essential for integration in modules covering PA, switch, LNA and filters for frequencies above 3.3GHz, thanks to its miniaturization capabilities.

Figure 6-25 Common Filter Technologies

### 6.2.2.3 Existing 3.3GHz-4.2GHz 5G Filter Products

### 1) Technological advantages of multilayer ceramic filters (LTCC)

With the utilization of multilayer ceramic technologies, it can provide extremely low insertion loss for Sub-6GHz while covering entire required bandwidth. The relative bandwidth that can be covered with multilayer ceramic filters is approximately from 5 to 50%. It also contributes to the downsizing and lower profile requirements with significantly stable performance and relatively low cost. This technology also provides rather high power handling capabilities in comparison with SAW technologies and this should be another advantage as HPUE should be required by 5G Sub-6GHz standard. On the other hand, multilayer ceramic filters provide rather relaxed skirt characteristics as opposed to SAW filter technology. This concept should directly be applied to 5G Sub-6GHz requirement including Band n77, n78 and n79.

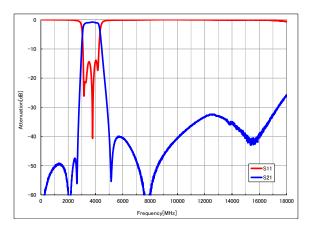

At the present, there is 5G LTCC filter already can support the HPUE device of Band n77 and Band n78, the main performance has been showed at below sheets and Table 6-3, Figure 6-26, Figure 6-4, Figure 6-27.

| Pass band Frequency  | 3.3GHz – 4.2GHz                        |                      |  |  |  |  |

|----------------------|----------------------------------------|----------------------|--|--|--|--|

| Insertion Loss(Type) | 1.29dB                                 |                      |  |  |  |  |

|                      | 600-2700MHz                            |                      |  |  |  |  |

| Attenuation(Type)    | 4900-5900MHz                           | 32.4dB               |  |  |  |  |

|                      | 6600-8400MHz                           | 44.1dB               |  |  |  |  |

|                      | 9900-12600MHz                          | 32.4dB               |  |  |  |  |

| Power Capability     | +33dBm at pass band frequency, 10000Hr |                      |  |  |  |  |

| Size                 | 2.0mm x 1.25mm x 0.65                  | 5mm MAX, LGA Package |  |  |  |  |

Table 6-3 Multilayer Ceramic Band Pass Filter for 5G NR Sub-6GHz Band n77 HPUE

Figure 6-26 Frequency performance of LTCC BPF for 5G NR Sub-6GHz Band n77 HPUE Note: Above actual test data is provided by TAIYO YUDEN.

| Pass band Frequency  | 3.3GHz –                                | 3.8GHz |  |  |  |  |

|----------------------|-----------------------------------------|--------|--|--|--|--|

| Insertion Loss(Type) | 1.54dB                                  |        |  |  |  |  |

| Attenuation(Type)    | 600-2700MHz                             | 46.5dB |  |  |  |  |

|                      | 4900-5900MHz                            | 39.2dB |  |  |  |  |

|                      | 6600-8400MHz                            | 42.6dB |  |  |  |  |

|                      | 9900-12600MHz 37.6dB                    |        |  |  |  |  |

| Power Capability     | +33dBm at pass band frequency,10000Hr   |        |  |  |  |  |

| Size                 | 2.0mm x 1.25mm x 0.65mm MAX,LGA Package |        |  |  |  |  |

Table 6-4 Multilayer Ceramic Band Pass Filter for 5G NR Sub-6GHz Band n78 HPUE

Figure 6-27 Frequency Performance of LTCC BPF for 5G NR Sub-6GHz Band n77 HPUE Note: Above simulation data is provided by TAIYO YUDEN.

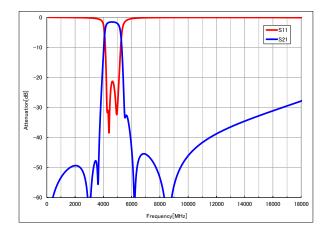

2) Integrated n77 filte

Below is integrated filter supporting 5G Band n77

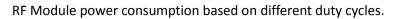

Figure 6-28 n77/n78 5G RF FEM Block Diagram

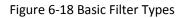

Tx chain gain data is as below

Figure 6-29 RF FEM Tx Gain Data

# 6.2.3 4.4GHz-5GHz 5G Filter Design

### 6.2.3.1 Design Challenges

3GPP RAN4 members have come to the agreement to choose the band from 4.4GHz to 4.99GHz earlier, on the other hand, as China MIIT (Ministry of Industry and Information Technology) published additional frequency ranges for 5G trial, including 4.8-5GHz. This was also proposed within 3GPP RAN4 and it has been approved that the upper edge of Band n79 was extended from 4.99GHz to 5GHz to support the spectrum demand in China. Within 3GPP, Band "n79" was newly assigned for "4.4-5GHz". Same as the filter for sub-6GHz 5G NR, the filters for 4.4-5GHz need to support wider frequency bandwidth and higher frequency. Other technology or integrated technologies shall be utilized depending upon the attenuation requirement of adjacent systems such as WiFi 5GHz and/or LAA/eLAA which starts at 5.15GHz.

### 6.2.3.2 Alternative Processes

Same as 6.2.2.2, LTCC technology is capable of meeting wider frequency bandwidth and higher frequency requirement.

### 6.2.3.3 Existing 4.4GHz-5GHz 5G Filter Products

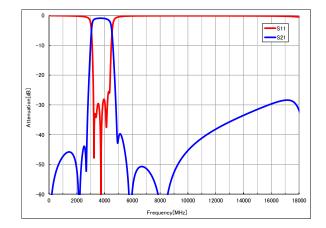

#### 1. Introduction of LTCC filter and related performance

Technology background of this Band n79 LTCC filter is same as previously explained in the article of Band n77 filter. LTCC based filter design is rather flexible and the design can be applied to other type devices including low pass filter, band pass filter, diplexer for Sub-6GHz in the light of upcoming 5G requirement. At present, Taiyo Yuden has been working on series of different band pass filters for 5G Band n79 and the following is the example from the variations and the size is 2.0mm x 1.25mm x 0.65mm Max with LGA (Land Grid Array) package and performance is as shown as below Table 6-5, Figure 6-30.

| Pass band Frequency  | 4.4GHz – 5GHz                          |                      |  |  |  |  |

|----------------------|----------------------------------------|----------------------|--|--|--|--|

| Insertion Loss(Type) | 2.09dB                                 |                      |  |  |  |  |

|                      | 100-915MHz                             | 54.0dB               |  |  |  |  |

| Attenuation(Type)    | 1427.9-1467MHz                         | 50.7dB               |  |  |  |  |

|                      | 2495-2690MHz                           | 50.9dB               |  |  |  |  |

|                      | 5490-5925MHz 31.2dB                    |                      |  |  |  |  |

| Power Capability     | +33dBm at pass band frequency, 10000Hr |                      |  |  |  |  |

| Size                 | 2.0mm x 1.25mm x 0.6                   | 5mm MAX, LGA Package |  |  |  |  |

Table 6-5 Multilayer Ceramic Band Pass Filter for Sub-6GHz 5G NR Band n79 HPUE

Figure 6-30 Frequency Performance of LTCC BPF for Sub-6GHz 5G NR Band n79 HPUE

Note: Above simulation data is provided by TAIYO YUDEN.

2. Integrated n79 filter

5G bands have higher frequency and wider band width, which requires filters provide more steep conversion bandwidth, these new requirements and characteristics bring great challenges to the existing acoustics based filters. The integrated passive filter which can be used in N79 device design provides a balance in performance, size and cost. Integrated n79 filter is still under development.

# 6.3 Sub-6GHz 5G Low Noise Amplifier

### 6.3.1 Existing Mobile Device Commercial Low Noise Amplifier

### Products

Broadband LNA is a critical component in radar, communication, electronic countermeasures, telemetry and remote areas. In wireless communication, the higher data transmission speed

requires the higher of channel capacity. For RF receiver, the noise figure and linearity of LNA directly affects and decides the sensitivity and dynamic range of a RF receiver, which requires LNA's low noise to improve the sensitivity and power gain, to reduce the noise of next level circuit.

### 6.3.2 Sub-6GHz 5G Low Noise Amplifier Design

### 6.3.2.1 Design Challenges

Wideband LNA design challenges are to keep high gain, low noise finger and high IP3 in the full band.

### 6.3.2.2 Alternative Processes

The processes for LNA include GaAs pHEMT, SiGe HBT and CMOS. SiGe HBT and CMOS with good compatibility and low cost, GaAs pHEMT has excellent noise and gain performance. GaAs pHEMT (E-mode) has the 2-D characteristic of the heterojunction, in order to get high carrier mobility and low noise figure.

1) 0.15um E-mode GaAs pHEMT

(E-mode) 0.15um GaAs pHEMT (E-mode) contains 17 masks and over 200 process steps. Each of these steps needs repeatable experiment, to ensure the whole process reliable and commercial

The domestic foundries are developing 6-inch 0.15um GaAs pHEMT technology, one choice of 5G's PA. The main performances of this technology are given in table 6-6.

| Item     | Unit   | Performance    | Condition        |

|----------|--------|----------------|------------------|

| TFR      | ohm/sq | 50+/-5         |                  |

| Lg       | um     | 0.150 +/- 0.02 |                  |

| Rs (Epi) | ohm/sq | 150 +/- 20     |                  |

| Idss     | mA/mm  | <0.05          | @Vgs=0V Vds=1.5V |

| Gm max   | mS/mm  | 1000 +/-150    |                  |

| Imax     | mA/mm  | 420 +/- 100    | @Vgs=+0.9V       |

| Vp       | V      | 0.3 +/- 0.15   | @1mA/mm          |

| BVgd     | V      | 10 +/- 3       | @1mA/mm          |

| ft       | GHz    | 110+/-25       |                  |

| Psat     | mW/mm  | > 700 mW/mm    | @29 GHz          |

The key parameters in table 6-6 are explained as follow:

- TFR: thin film resistor, produced by TaN.

- Lg: gate length, the smaller Lg , the higher Ft.

- Rs(Epi): epitaxy active layer resistor.

- Idss: the drain current.

- Gm\_max: the maximum value of the transconductance.

- Idmax: the maximum value of the drain current.

- Vp: the gate threshold voltage. The gate voltage is larger than Vp, the transistor is switched on; the gate voltage is smaller than Vp, the transistor is switched off.

- BVgd: the drain-source breakdown voltage.

- ft: the cut off frequency.

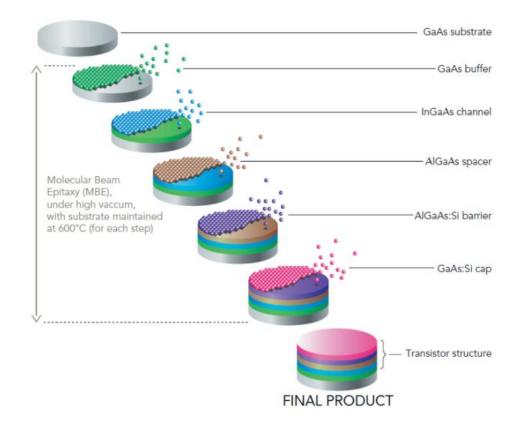

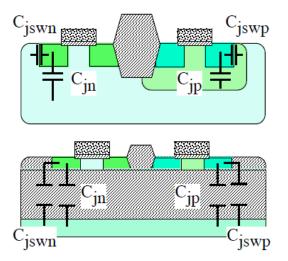

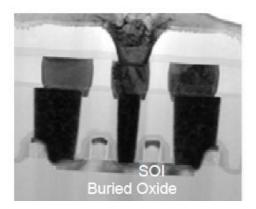

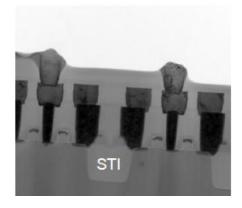

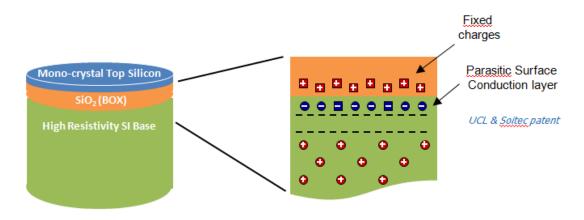

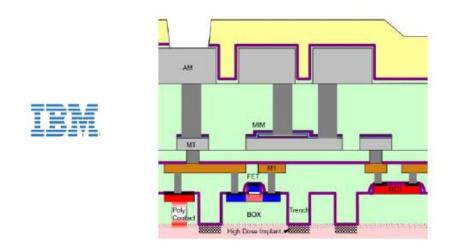

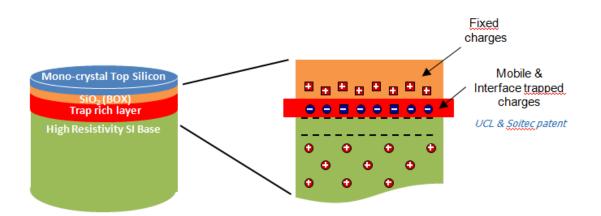

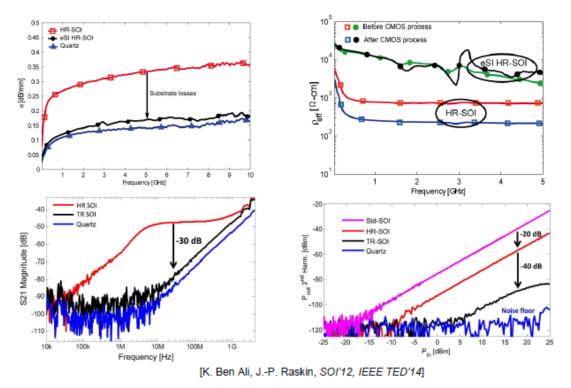

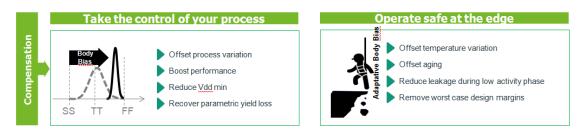

- 2) 0.25um E-mode GaAs pHEMT