# GTI 5G S-Module White Paper

### GTI 5G S-ModuleWhite Paper

| Version:                | V2.1                                               |

|-------------------------|----------------------------------------------------|

| Deliverable Type        | □ Procedural Document                              |

|                         | √ Working Document                                 |

| Confidential Level      | √Open to GTI Operator Members                      |

|                         | √Open to GTI Partners                              |

|                         | □ Open to Public                                   |

| Program                 | 5G eMBB                                            |

| Working Group           | Terminal WG                                        |

| Project                 | Project 3: New Device                              |

| Task                    | 5G S-Module Task Force                             |

| Source members          | China Mobile, Sprint                               |

|                         | SIMCom, Fibocom, Quectel, Hisense, Cheerzing       |

|                         | Qorvo, Taiyo Yuden, Murata, Sunway                 |

|                         | Anritsu, Keysight, Rohde & Schwarz                 |

| Support members         | HP, Lenovo, Xiaomi                                 |

| (in alphabetical order) | Huawei                                             |

|                         | Hisilicon, Intel, MTK, Qualcomm, Sanechips, Unisoc |

|                         | Lansus, Macom, Skyworks, SmarterMicro, Vanchip     |

|                         | Starpoint                                          |

| Last Edit Date          |                                                    |

| Approval Date           |                                                    |

Confidentiality: This document may contain information that is confidential and access to this document is restricted to the persons listed in the Confidential Level. This document may not be used, disclosed or reproduced, in whole or in part, without the prior written authorization of GTI, and those so authorized may only use this document for the purpose consistent with the authorization. GTI disclaims any liability for the accuracy or completeness or timeliness of the information contained in this document. The information contained in this document may be subject to change without prior notice.

# Document History His

| Date          | Meeting #                        | Version # | Revision Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|----------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oct. 31, 2018 | 23 <sup>rd</sup> GTI<br>Workshop | V1.0      | The first version of GTI 5G S-Module Whitepaper. The standardization status of 5G universal modules, the industry status of 5G S-Modules and the typical technology solutions for 5G S-Modules are described.                                                                                                                                                                                                                                                                                                                                                                                   |

| Feb.19, 2019  | Workshop                         | V1.1      | Some revisions have been made to Section "8.2.2 Pin Layout" and "8.2.3 Pin Size" of "GTI 5G S-Module Whitepaper (v1.0)" as per the industry R&D progress.  Section "8.3.2 Pin Layout" and "8.3.4 Pin Definition" have been updated. Some pins have been clarified as "/Reserved" also. Some misalignments between "8.3.2 Pin Layout" and "8.3.4 Pin Definition" have been fixed.                                                                                                                                                                                                                |

| Jun. 21, 2019 | 25 <sup>th</sup> GTI<br>Workshop | V2.0      | The original "5G S-Module Basic Type 1" and "5G S-Module Basic Type 2" have been merged as "5G S-Module Basic Type-L" as per the latest industry R&D progress.  The original "5G S-Module Basic Type 3" has been renamed as "5G S-Module Basic Type-M".  Section "5.2.2.1 Modes and Bands" has been updated.  Section "6 The Industry Status" has been updated as per the latest progress of the industry.  Section "8.4 5G S-Module All-in-one Type-M", Section "8.5 5G S-Module All-in-one Type-L" and Section "11 Typical Application Scenarios for 5G S-Module" have been added.            |

| Nov. 1, 2019  | 26 <sup>th</sup> GTI<br>Workshop | V2.1      | A new kind of 5G S-Module basic type-L (Layout 3) is added in section 8.1. A new kind of 5G S-Module basic type-L is added in section 8.1A. Section "6 The Industry Status" has been updated as per the latest progress of the industry. The diagram of 5G S-Module Basic Type-L in section 8.1.1 is updated. The pin layouts of 5G S-Module basic type-L in section 8.1.2 and the pin size of 5G S-Module basic type-L in section 6.1.3 are updated. The pin definition of 5G S-Module basic type-L is updated and a new pin definition of 5G S-Module basic type-L is added in section 8.1.4. |

| The pin layout of 5G S-Module Basic Type-m is     |

|---------------------------------------------------|

| updated in section 8.2.2.                         |

| The pin definition of 5G S-Module Basic Type-m is |

| updated in section 8.2.4.                         |

| Module power current in power off mode in         |

| section 9.1.1 is updated.                         |

| Setup of ADC in section 9.6.1 is updated.         |

### **Table of Contents**

| GTI  | 5G S   | -Module           | White Paper                              | 2  |  |  |

|------|--------|-------------------|------------------------------------------|----|--|--|

| Doc  | ume    | ent History       |                                          |    |  |  |

| Tabl | e of ( | f Contents        |                                          |    |  |  |

| 1    | Exe    | ecutive Summary10 |                                          |    |  |  |

| 2    | Refe   | erences           |                                          | 11 |  |  |

| 3    | Abb    | reviatio          | ns                                       | 12 |  |  |

| 4    | Intr   | oductior          | ١                                        | 17 |  |  |

| 5    | The    | Standar           | dization Status                          | 19 |  |  |

|      | 5.1    |                   | vation                                   |    |  |  |

|      | 5.2    | Stand             | dardization of 5G S-Module               |    |  |  |

|      |        | 5.2.1             | The Diagram of 5G S-Module               | 20 |  |  |

|      |        | 5.2.2             | The Key Points to classify 5G S-Module   |    |  |  |

| 6    | The    | Industry          | y Status                                 | 23 |  |  |

|      | 6.1    |                   | ndustry Status of 4G Module              |    |  |  |

|      | 6.2    | How               | to make 5G S-Module?                     | 26 |  |  |

|      | 6.3    | The I             | ndustry Status of 5G Chipset             | 26 |  |  |

|      | 6.4    | The I             | ndustry Status of 5G Module              | 27 |  |  |

|      | 6.5    |                   | ndustry Status of 5G Device              |    |  |  |

| 7    | The    |                   | nctions Requirements on 5G S-Module      |    |  |  |

|      | 7.1    | Mana              | agement Functions                        |    |  |  |

|      |        | 7.1.1             | Identity Management                      |    |  |  |

|      |        | 7.1.2             | Status Management                        | 28 |  |  |

|      |        | 7.1.3             | Parameter Preset Management              |    |  |  |

|      | 7.2    |                   | -unctions                                |    |  |  |

|      | 7.3    | Debu              | g Functions                              | 29 |  |  |

|      | 7.4    |                   | ware Upgrade Functions                   |    |  |  |

| 8    | The    | Hardwa            | re Technical Requirements on 5G S-Module | 30 |  |  |

|      | 8.1    | 5G S-             | Module Basic Type-L                      | 31 |  |  |

|      |        | 8.1.1             | Diagram                                  | 31 |  |  |

|      |        | 8.1.2             | Pin Layout                               | 31 |  |  |

|      |        | 8.1.3             | Pin Size                                 | 34 |  |  |

|      |        | 8.1.4             | Pin Definition                           | 38 |  |  |

|      | 8.1    | 4 5G S-           | -Module Basic Type-L                     | 61 |  |  |

|      |        | 8.1A.1            | Diagram                                  | 61 |  |  |

|      |        | 8.1A.2            | Pin Layout                               | 62 |  |  |

|      |        | 8.1A.3            | Pin Size                                 | 62 |  |  |

|      |        | 8.1A.4            | Pin Definition                           | 64 |  |  |

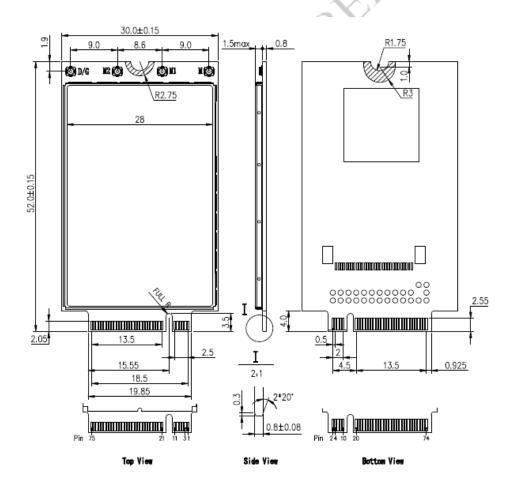

|      | 8.2    | 5G S-             | Module Basic Type-M                      | 74 |  |  |

|      |        | 8.2.1             | Diagram                                  | 74 |  |  |

|   |     | 8.2.2  | Pin Layout                                         | 74  |

|---|-----|--------|----------------------------------------------------|-----|

|   |     | 8.2.3  | Pin Size                                           | 76  |

|   |     | 8.2.4  | Pin Definition                                     | 77  |

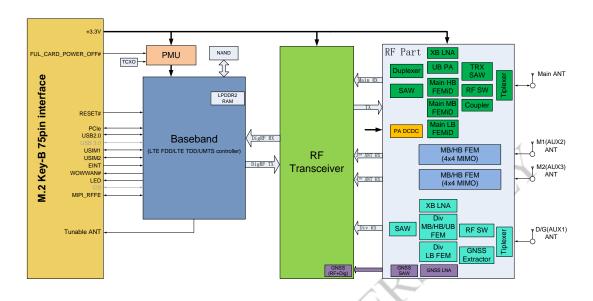

|   | 8.3 | 5G S-  | Module Smart Type                                  | 80  |

|   |     | 8.3.1  | Diagram                                            | 80  |

|   |     | 8.3.2  | Pin Layout                                         | 82  |

|   |     | 8.3.3  | Pin Size                                           | 83  |

|   |     | 8.3.4  | Pin Definition                                     | 84  |

|   | 8.4 | 5G S-  | Module All-in-one Type-M                           | 89  |

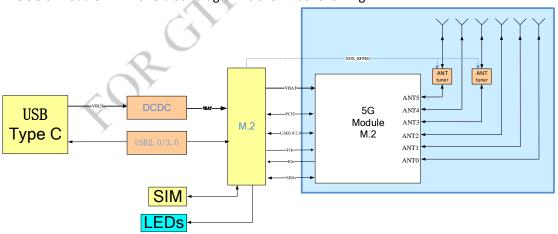

|   |     | 8.4.1  | Diagram                                            | 89  |

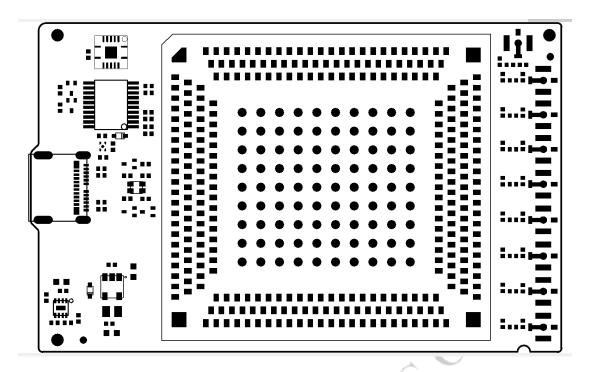

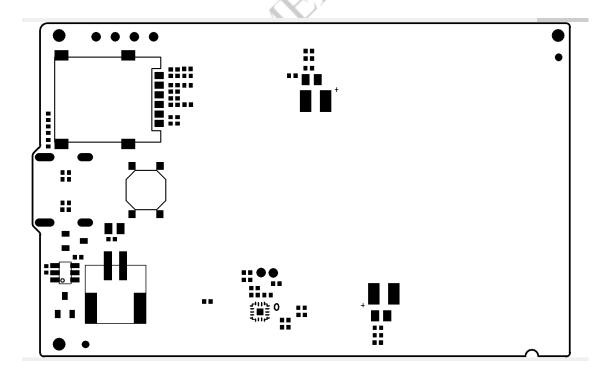

|   |     | 8.4.2  | PCB Layout                                         | 90  |

|   |     | 8.4.3  | PCB Size                                           |     |

|   |     | 8.4.4  | Pin Definition                                     |     |

|   | 8.5 | 5G S-  | Module All-in-one Type-L                           |     |

|   |     | 8.5.1  | Diagram                                            |     |

|   |     | 8.5.2  | PCB Layout                                         |     |

|   |     | 8.5.3  | PCB Size                                           |     |

|   |     | 8.5.4  | Pin Definition                                     | 95  |

| 9 | The |        | al Interface Technical Requirements on 5G S-Module |     |

|   | 9.1 |        | r Supply Interface                                 |     |

|   |     | 9.1.1  | Power Supply                                       |     |

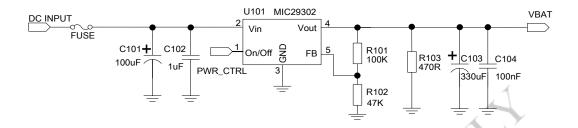

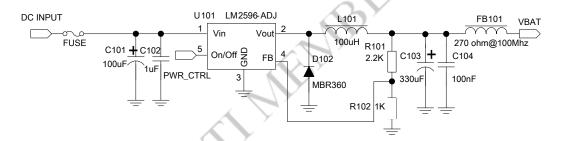

|   |     | 9.1.2  | Power Supply Design Guide                          | 98  |

|   |     | 9.1.3  | Recommended Power Supply Circuit                   |     |

|   | 9.2 | Modu   | ule Control and Status Interface                   |     |

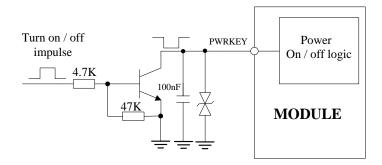

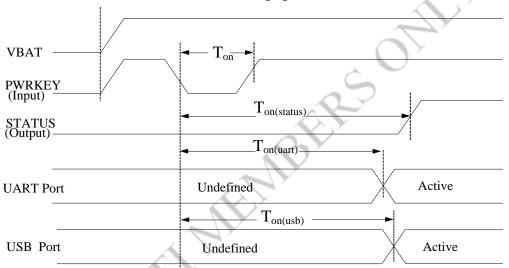

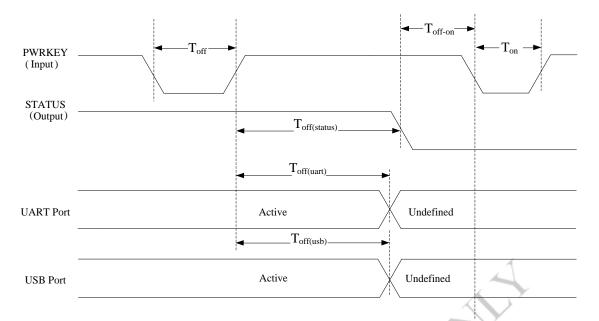

|   |     | 9.2.1  | Power On                                           |     |

|   |     | 9.2.2  | Power Off                                          | 100 |

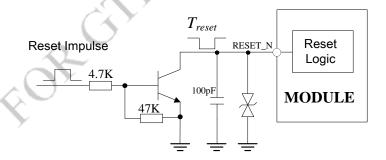

|   |     | 9.2.3  | Reset Function                                     |     |

|   | 9.3 | RF Int | terface                                            | 101 |

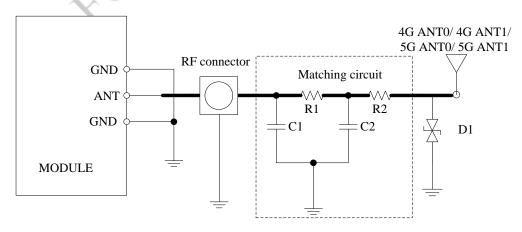

|   |     | 9.3.1  | GSM /UMTS/LTE/5G sub-6GHz Antenna Design Guide     | 101 |

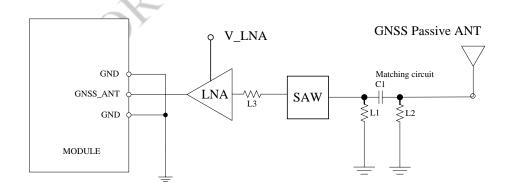

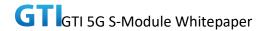

|   |     | 9.3.2  | GNSS Application Guide                             | 103 |

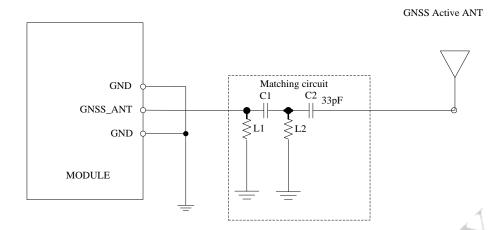

|   |     | 9.3.3  | Wi-Fi/BT Application Guide                         |     |

|   | 9.4 | SIM II | nterface                                           |     |

|   |     | 9.4.1  | USIM Application Guide                             |     |

|   | 9.5 | Data   | I/O Interface                                      | 107 |

|   |     | 9.5.1  | 4-wire UART                                        | 107 |

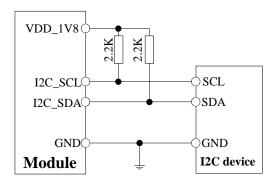

|   |     | 9.5.2  | I2C Interface                                      | 107 |

|   |     | 9.5.3  | SPI Interface                                      | 108 |

|   | 9.6 | Analo  | og Interface                                       | 108 |

|   |     | 9.6.1  | ADC                                                |     |

|   | 9.7 | Audio  | o Interface                                        |     |

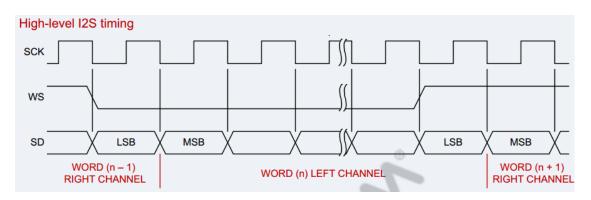

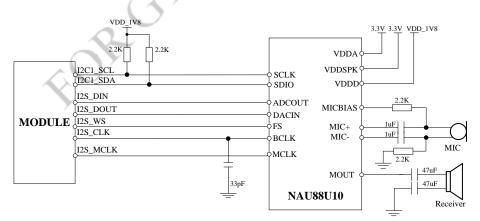

|   |     | 9.7.1  | I2S Interface                                      |     |

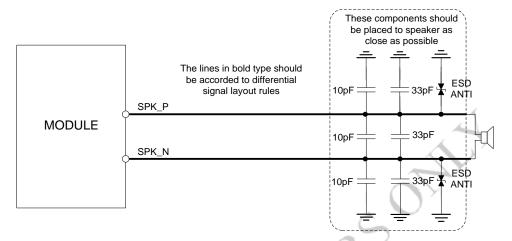

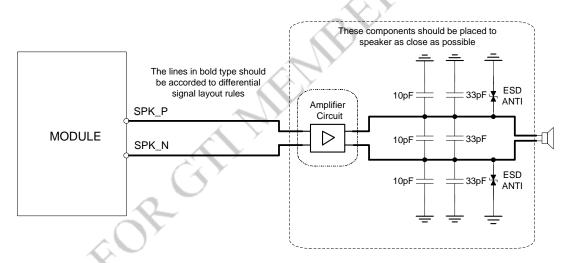

|   |     | 9.7.2  | Speaker Interface Configuration                    |     |

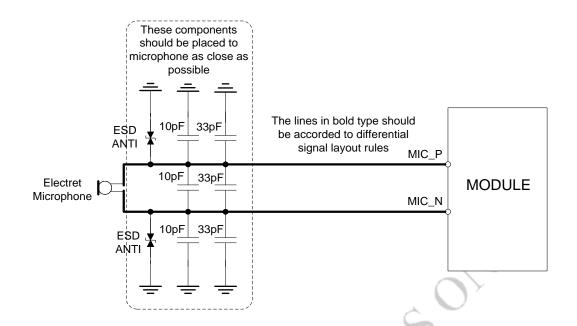

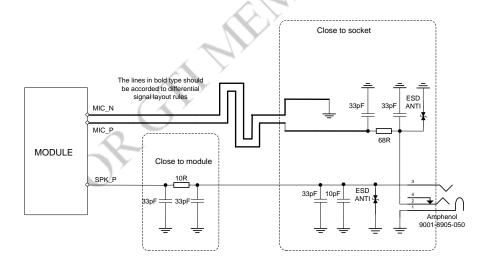

|   |     | 9.7.3  | Microphone Interfaces Configuration                | 112 |

|     | 9.7.4        | Earphone Interface Configuration           | 112  |

|-----|--------------|--------------------------------------------|------|

| 10  | The Test and | d Certification of 5G S-Module             | 113  |

|     | 10.1 Lab C   | Onformance Test                            | 113  |

|     | 10.1.1       | GCF Testing                                | 116  |

|     | 10.1.2       | PTCRB Testing                              | 118  |

|     | 10.2 Field   | Test                                       | 118  |

|     | 10.3 Indus   | stry Regulatory Test                       | 120  |

|     | 10.3.1       | Regulatory Testing                         | 120  |

|     | 10.4 Carrie  | er Acceptance Test                         | 122  |

| 11  | Typical Appl | ication Scenarios for 5G S-Module          | 123  |

|     | 11.1 5G S-   | Module Basic Type-L                        | 123  |

|     | 11.1.1       | Smart Factory – Robot                      | 123  |

|     | 11.1.2       | Connected Energy – Industrial Routers      | 124  |

|     | 11.1.3       | UHD 8K Online Video & living broadcast     | 125  |

|     | 11.1.4       | Wireless eHealth                           | 125  |

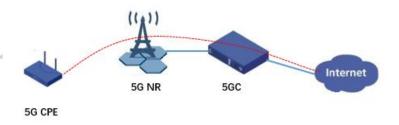

|     | 11.1.5       | FWA                                        | 126  |

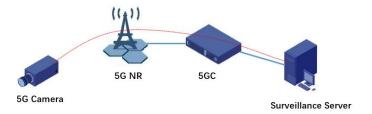

|     | 11.1.6       | Video Surveillance                         | 126  |

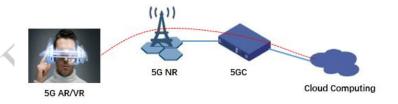

|     | 11.1.7       | AR/VR                                      | 127  |

|     | 11.2 5G S-   | Module Basic Type-M                        | 127  |

|     | 11.2.1       | Laptop industry and sky office application | 127  |

|     | 11.3 5G S-   | Module Smart Type                          | 128  |

|     | 11.3.1       | Smart POS                                  | 128  |

|     | 11.3.2       | Connected Automotive                       | 129  |

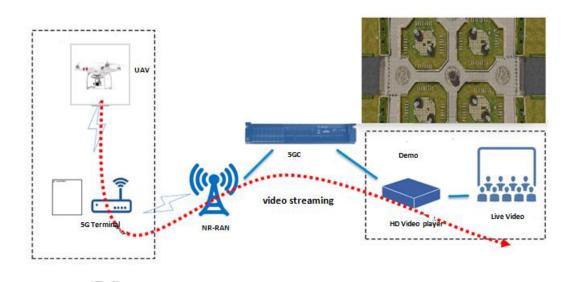

|     | 11.3.3       | Connected Drones                           | 130  |

|     | 11.4 5G S-   | Module All-in-one Type-M and Type-L        | 130  |

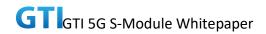

|     | 11.4.1       | USB Dongle                                 | 130  |

| Ann | ex A 50      | G RF Component                             | 131  |

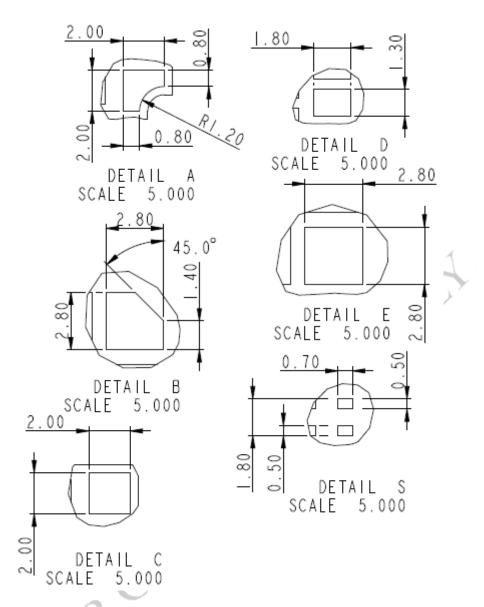

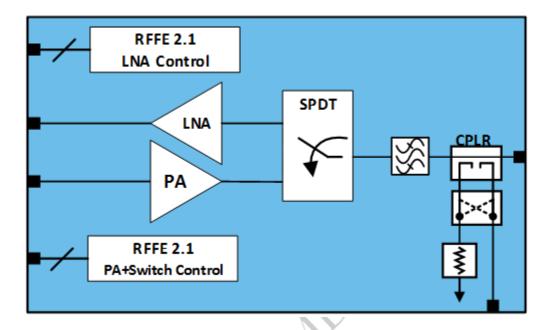

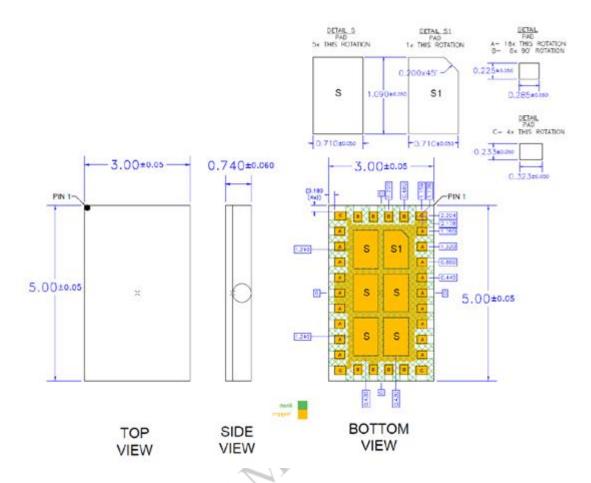

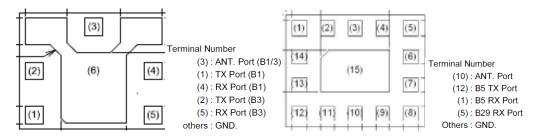

|     | Annex A.1    | 5G RF FEM Type1 (Separated n41 and n79)    | 131  |

|     | Annex        | A.1.1 Diagram                              | 131  |

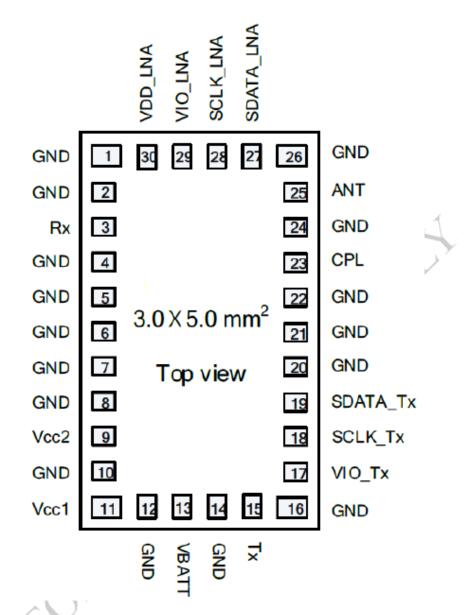

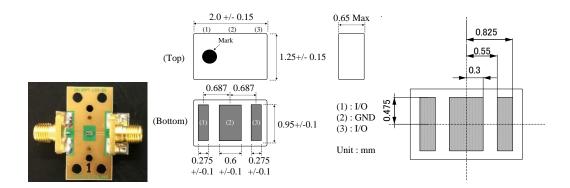

|     | Annex        | A.1.2 Pin Layout                           | 133  |

|     | Annex        | A.1.3 Pin Size                             | 134  |

|     | Annex A.2    | 5G RF FEM Type2 (n41)                      | 134  |

|     | Annex        | A.2.1 Diagram                              | 134  |

|     | Annex        | A.2.2 Pin Layout                           | 136  |

|     | Annex        | A.2.3 Pin Size                             | 137  |

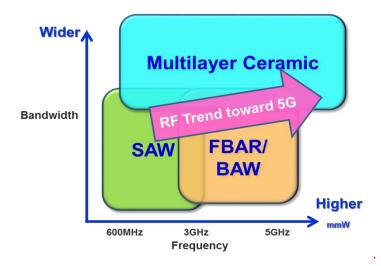

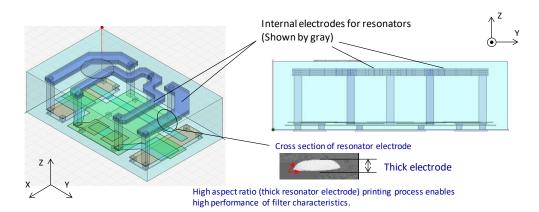

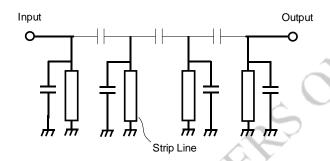

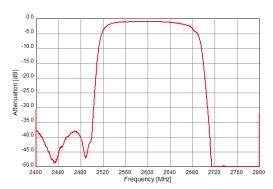

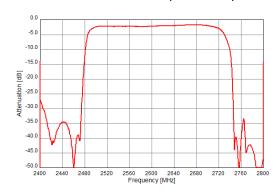

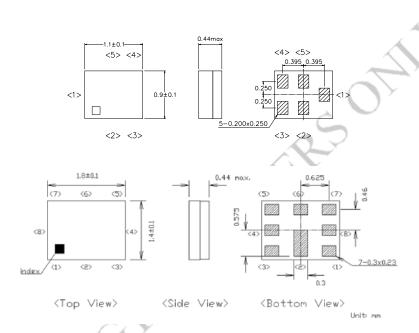

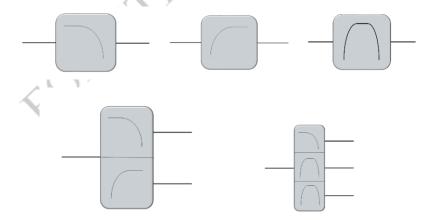

|     | Annex A.3    | 5G LTCC/SAW/FBAR Filters                   | 137  |

|     | Annex        | A.3.1 Diagram                              | 138  |

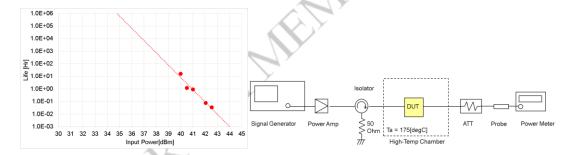

|     | Annex        | A.3.2 Pin Layout, Pin Size, Pin Definition | 139  |

|     | Annex        | A.3.3 High power handling                  | 139  |

|     | Annex        |                                            |      |

|     | Annex        |                                            |      |

|     | Annex A.4    | 5G SAW Filters                             |      |

|     | Annov        | Δ / 1 Diagram                              | 1/11 |

|         | Annex A.4.2 | Pin Layout                         | 142 |

|---------|-------------|------------------------------------|-----|

|         | Annex A.4.3 | 3 Pin Size                         | 142 |

|         | Annex A.4.  | Pin Definition                     | 143 |

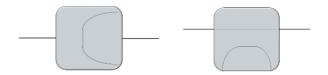

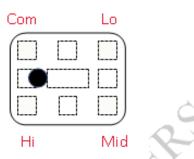

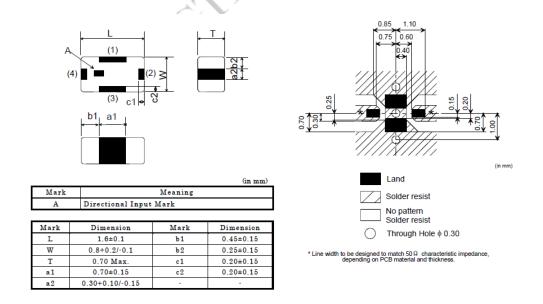

| Ann     | ex A.5 5    | G LTCC Components                  | 144 |

|         | Annex A.5.  | L Diagram                          | 144 |

|         | Annex A.5.2 | Pin Layout                         | 145 |

|         | Annex A.5.3 | 3 Pin Size                         | 145 |

|         | Annex A.5.  | Pin Definition                     | 146 |

| Annex B | Anten       | na for 5G S-Module                 | 147 |

| Ann     | ex B.1 A    | ntennas for S-Module Basic Type    | 147 |

|         | Annex B.1.2 | Diagram                            | 147 |

|         | Annex B.1.2 | 2 Antennas connected to the module | 147 |

|         | Annex B.1.3 |                                    | 148 |

| Ann     | ex B.2 A    | ntenna for S-Module Smart Type     |     |

|         | Annex B.2.2 | -0 -                               | 149 |

|         | Annex B.2.2 |                                    |     |

|         | Annex B.2.3 |                                    |     |

| Annex C | Senso       | ensor Technology                   | 153 |

| Ann     | ex C.1 S    | ensor Technology                   | 153 |

| Ann     | ex C.2 C    | utting-edge Sensor Application     | 154 |

| Δnn     | exC3 T      | ne Universal Interfaces of Sensors | 155 |

FORCIFILME

### 1 Executive Summary

This white paper provides a technical overview of the **5G Superior Universal Module**, which is known as "**5G S-Module**". It covers the industry status, the requirement, and the technology for 5G S-Module.

5G Technology has three typical scenarios: eMBB, mMTC, and URLLC, which bring a number of enhancements including ultra-high speeds, large quantity of connection, ultra-low latencies, high performance, enhanced reliability and low power consumption. eMBB brings high throughput for the 5G devices, which increases the network efficiency and performance. Our 5G S-Module will start with the application for the eMBB scenario.

In 5G network, there is a "network slicing" characteristic. It creates the possibility of tailoring mobile data services for the particular characteristics of specific users. For example, a dense grid network might prioritize low power consumption of massive terminals over connection speed; at the same time, a separate network slice on the same infrastructure could provide high-speed mobile communications for specific application. "Network slicing" will help 5G S-Module to use the network resources efficiently.

Network slicing ability for different services on the same physical networks raises the possibility of services targeted at different industrial verticals. Here we also analyze the status of the vertical market, the different requirement of the different verticals. For a particular industry, it may need specific attributes of the 5G S-Module, therefore, we categorize the requirements together and extract a generic requirement for the 5G S-Module. In general, the 5G S-Module will fulfill the requirements of different industry verticals.

The 5G S-Module solution helps the industry to finish their 5G capable device development easily, and makes it possible for a "turnkey" solution for different applications. The industries with embedded modules are always quite segmented. With 5G S-Module, it could meet the most industry requirements and operates at high-performance, benefiting from the 5G NR technology.

### 2 References

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- [1] http://resources.mipi.org/mipi-i3c-v1-download

- [2] 3GPP, TS 38.101-1, NR; User Equipment (UE) radio transmission and reception; Part 1: Range 1 Standalone.

- [3] 3GPP, TS 38.101-2, NR; User Equipment (UE) radio transmission and reception; Part 2: Range 2 Standalone.

- [4] 3GPP, TS 38.101-3, NR; User Equipment (UE) radio transmission and reception; Part 3: Range 1 and Range 2 Interworking operation with other radios.

- [5] 3GPP, TS 38.101-4, NR; User Equipment (UE) radio transmission and reception; Part 4: Performance requirements.

- [6] 3GPP, TS 38.521-1, NR; User Equipment (UE) conformance specification; Radio transmission and reception; Part 1: Range 1 Standalone.

- [7] 3GPP, TS 38.521-2, NR; User Equipment (UE) conformance specification; Radio transmission and reception; Part 2: Range 2 Standalone.

- [8] 3GPP, TS 38.521-3, NR; User Equipment (UE) conformance specification; Radio transmission and reception; Part 3: Range 1 and Range 2 Interworking operation with other radios.

- [9] 3GPP, TS 38.521-4, NR; User Equipment (UE) conformance specification; Radio transmission and reception; Part 4: Performance.

- [10] 3GPP, TS 38.523-1, 5GS; UE conformance specification; Part 1: Protocol.

- [11] 3GPP, TS 38.523-2, 5GS; UE conformance specification; Part 2: Applicability of protocol test cases.

- [12] 3GPP, TS 38.523-3, 5GS; User Equipment (UE) conformance specification; Part 3: Protocol Test Suites.

- [13] 3GPP, TS 38.533, NR; User Equipment (UE) conformance specification; Radio Resource Management (RRM)

- [14] GTI, GTI Sub-6GHz 5G Device Whitepaper (v3.0)

- [15] GSA, LTE, 5G and 3GPP IoT Chipsets: Status Update, July 2019

- [16] GSA, 5G Device Ecosystem, September 2019

### 3 Abbreviations

| Abbreviation | Explanation                                     |

|--------------|-------------------------------------------------|

| 3GPP         | 3rd Generation Partnership Project              |

| ACPC         | Always Connected Personal Computer              |

| ADC          | Analog-to-Digital Converter                     |

| Al           | Analog Input                                    |

| AIO          | Analog Input/ Output                            |

| AO           | Analog Output                                   |

| AP           | Application Processor                           |

| APN          | Access Point Name                               |

| APT          | Average Power Tracking                          |

| AR           | Augmented Reality                               |

| BD           | BeiDou                                          |

| BOM          | Bill of Material                                |

| ВР           | Baseband Processor                              |

| BPF          | Band-Pass Filter                                |

| BT           | Blue Tooth                                      |

| CCTV         | China Central TeleVision                        |

| CHAP         | Challenge Handshake Authentication Protocol     |

| CMCC         | China Mobile Communications Corporation         |

| CMOS         | Complementary Metal Oxide Semiconductor         |

| СРЕ          | Customer Premise Equipment                      |

| CPRL         | CommandLine Uniform Resource Locator            |

| CPU          | Central Processing Unit                         |

| CRM          | Customer relationship management                |

| C-V2X        | Cellular,vehicle-to-everything                  |

| DCC          | Device Certification Criteria                   |

| DCDC         | Direct Current/Direct Current                   |

| DDR          | Double Data Rate                                |

| DI           | Digital Input                                   |

| DIO          | Digital Input/ Output                           |

| DL           | Down Link                                       |

| DO           | Digital Output                                  |

| еМВВ         | Enhanced Mobile Broadband                       |

| EMC          | Electro Magnetic Compatibility                  |

| eMBMS        | Evolved Multimedia Broadcast Multicast Services |

| еММС         | Embedded Multi-Media Card                       |

| ET      | Envelop Tracking                                   |

|---------|----------------------------------------------------|

|         |                                                    |

| eUICC   | Embedded Universal Integrated Circuit Card         |

| ESD     | Electro-Static Discharge                           |

| ESR     | Errored Second Ratio                               |

| ETSI    | The European Telecommunication Standards Institute |

| FBAR    | thin Film Bulk Acoustic Resonator                  |

| FCC     | Federal Communications Commission                  |

| FDD     | Frequency Division Duplex                          |

| FEM     | Front-End Module                                   |

| FM      | Frequency Modulation                               |

| FOTA    | Firmware Over-The-Air                              |

| GCF     | Global Certification Forum                         |

| GLONASS | GLObal NAvigation Satellite System                 |

| GNSS    | Global Navigation Satellite System                 |

| GPIO    | General Purpose I/O                                |

| GPRS    | General Packet Radio Service                       |

| GPS     | Global Positioning System                          |

| GSA     | Global mobile Suppliers Association                |

| GSM     | Global System for Mobile communications            |

| GSMA    | Global System for Mobile communications Alliance   |

| GTI     | Global TD-LTE Initiative                           |

| HPF     | High-Pass Filter                                   |

| HPUE    | High Power User Equipment                          |

| I2C     | Inter-Integrated Circuit                           |

| 125     | Integrated Interchip Sound                         |

| IF      | Intermediate Frequency                             |

| IMEI    | International Mobile Equipment Identity            |

| IMSI    | International Mobile Subscriber Identity           |

| IMT     | International Mobile Telecommunication             |

| IMU     | Inertial Measurement Unit                          |

| IoT     | Internet of Things                                 |

| IP      | Internet Protocol                                  |

| ITU     | International Telecommunication Union              |

| ITU-R   | International Telecommunication Union - Radio      |

| LCC     | Leadless Chip Carriers                             |

| LCD     | Liquid Crystal Display                             |

| LDO     | Low Dropout Regulator                              |

| LED     | Light Emitting Diode                               |

| LGA     | Land Grid Array                                    |

| LNA     | Low Noise Amplifier                                |

| LPDRAM  | Low-Power Dynamic RAM                              |

| LPF     | Low-Pass Filter                                    |

| -       |                                                    |

| LTCC  | Low Temperature Co-Fired Ceramic              |

|-------|-----------------------------------------------|

| LTE   | Long Term Evolution                           |

| M2M   | Machine to Machine                            |

| MCU   | Micro-Controller Unit                         |

|       | MoDule Controller                             |

| MDC   |                                               |

| MDIO  | Management Data Interface                     |

| MIMO  | Multi-input Multi-output                      |

| MIPI  | Mobile Industry Processor Interface           |

| MLCC  | Multi-Layer Ceramic Chip                      |

| MNO   | Mobile Network Operator                       |

| MUX   | MUltipleX(er)                                 |

| MWC   | Mobile World Congress                         |

| NC    | Not Connect                                   |

| NMEA  | National Electrical Manufacturers Association |

| NR    | New Radio                                     |

| NSA   | Non StandAlone                                |

| OAM   | Operation, Administration and Maintenance     |

| OD    | Open-Drain                                    |

| ODU   | Outdoor Unit                                  |

| OEM   | Original Equipment Manufacturer               |

| ODM   | Original Design Manufacturer                  |

| OS    | Operating System                              |

| PA    | Power Amplifier                               |

| PAP   | Password Authentication Protocol              |

| PC    | Personal Computer                             |

| PCB   | Printed Circuit Board                         |

| PCI   | Peripheral Component Interconnect             |

| PCIe  | Peripheral Component Interconnect express     |

| PCM   | Pulse-Code Modulation                         |

| PI    | Power In                                      |

| PMIC  | Power Management Integrated Circuit           |

| PMU   | Power Management Unit                         |

| POS   | Point Of Sales                                |

| PPS   | Pulse Per Second                              |

| PTCRB | PCS Type Certification Review Board           |

| PWM   | Pulse Width Modulation                        |

| QoS   | Quality of Service                            |

| R&D   | Research and Development                      |

| RAM   | Random Access Memory                          |

| RAN   | Radio Access Network                          |

| RED   | Radio Equipment Directive                     |

| RF    | Radio Frequency                               |

|       |                                               |

| RFFE   | RF Front-End                                |

|--------|---------------------------------------------|

| RGB    | Red-Green-Blue                              |

| RGMII  |                                             |

| ROM    | Reduced Gigabit Media Independent Interface |

| RRM    | Read-Only Memory  Radio Resource Management |

|        | 1                                           |

| RX     | Receive                                     |

| SA     | StandAlone Surface Accustic Mana            |

| SAW    | Surface Acoustic Wave                       |

| SD     | Secure Digital Memory Card                  |

| SDC    | Serial Data Controller                      |

| SDIO   | Secure Digital Input/Output                 |

| SHD    | Super High Definition Display               |

| SIM    | Subscriber Identification Module            |

| SMD    | Surface Mount Technology                    |

| SMEs   | small and medium-sized enterprises          |

| SMS    | Short Messaging Service                     |

| SoC    | System-on-a-Chip                            |

| SPDT   | Single Pole Double Throw                    |

| SPI    | Serial Peripheral Interface                 |

| STB    | Set Top Box                                 |

| TD-LTE | Time Division Long Term Evolution           |

| TDD    | Time Division Duplex                        |

| TIS    | Total Isotropic Sensitivity                 |

| TR     | Technology Report                           |

| TRP    | Total Radiated Power                        |

| TTCN   | Testing and Test Control Notation           |

| TTFF   | Time to First Fix                           |

| TX     | Transmit                                    |

| UART   | Universal Asynchronous Receiver/Transmitter |

| UAV    | Unmanned Air Vehicle                        |

| UE     | User Equipment                              |

| UHD    | Ultra High Definition                       |

| UL     | Up Link                                     |

| URL    | Uniform Resource Location                   |

| USB    | Universal Serial Bus                        |

| USIM   | UMTS Subscriber Identity Module             |

| USSD   | Unstructured Supplementary Service Data     |

| V2I    | Vehicle-to-Infrastructure                   |

| V2V    | Vehicle-to-Vehicle                          |

| VR     | Virtual Reality                             |

| WCDMA  | Wideband Code Division Multiple Access      |

| WLAN   | Wireless Local Area Network                 |

| L      | I                                           |

| WWAN Wireless Wide Area Networks |

|----------------------------------|

|----------------------------------|

FOR CHILDREN BERSON IN THE STATE OF THE STAT

### 4 Introduction

SIMCom, Fibocom, Quectel

This whitepaper mainly focuses on the 5G S-Module and has been carried out in several sections in turn. Combined with the standardization status and the industry status of 5G S-Module, the whitepaper analyses the required basic functions, the hardware technical requirements, the electrical interface technical requirements, test & certification and the typical technical solutions for 5G S-Module. For the communication capability, please refer to the "GTI Sub-6GHz 5G Device Whitepaper". This GTI 5G S-Module Whitepaper is expected to help people to develop 5G S-Modules and to promote 5G industrial development especially in verticals. This whitepaper may also help people to know more about the standardization status and industrial status of 5G S-Module. Meanwhile, it may also help readers interested in 5G S-Modules and vertical devices to gain from the further thinking.

Sincere thanks to all the contributors and the supporters for their hard work in writing this whitepaper, so we are respectfully listing them in alphabetical order under every chapter.

| • |                                              | Chapter 1 Executive Summary                          |

|---|----------------------------------------------|------------------------------------------------------|

|   | CMCC, SIMCom                                 |                                                      |

| • |                                              | Chapter 2 Reference                                  |

| • |                                              | Chapter 3 Abbreviations                              |

|   | CMCC                                         |                                                      |

| • |                                              | Chapter 4 Introduction                               |

|   | CMCC                                         | A.                                                   |

| • |                                              | Chapter 5 The Standardization Status                 |

|   | CMCC, Quectel, Sprint                        |                                                      |

| • |                                              | Chapter 6 The Industry Status                        |

|   | Fibocom, Cheerzing                           |                                                      |

| • |                                              | Chapter 7 The Basic functions Requirements on 5G     |

|   | S-Module                                     |                                                      |

|   | Hisense                                      |                                                      |

| • |                                              | Chapter 8 The Hardware Technical Requirements on     |

|   | 5G S-Module                                  |                                                      |

|   | SIMCom, Fibocom, Quectel, CMIOT              |                                                      |

| • |                                              | Chapter 9 The Electrical Interface Technical         |

|   | Requirements on 5G S-Module                  |                                                      |

|   | SIMCom                                       |                                                      |

| • |                                              | Chapter 10 The Test and Certification of 5G S-Module |

|   | Anritsu, CMCC, Keysight, R&S, SIMCom, Sprint |                                                      |

Chapter 11 Typical Technical Solutions for 5G S-Module

**Annex A 5G RF Component**

Qorvo, Taiyo Yuden, Murata

Annex B Antenna

Sunway

Annex C Sensor

SIMCom, Sprint

Special thanks to the following contributors for writing the whitepaper.

China Mobile

Dr. Dan Song, Mr. Xiaofeng Peng, Dr. Xiaoxiong Song, Mr. Shuai Ma, Mr. Shanpeng Xiao and Dr. Guangyi Liu

• Sprint

Mr. Zheng Fang, Mr. Michael Witherell

• SIMCom

Dr. Diane Lu

• Fibocom

Mr. Shawn Zhu, Mr. Jianguo Zhang

• Quectel

Mr. Albert Deng, Mr. Raki Zhang

• Hisense

Dr. Lujuan Ma

Cheerzing

Dr. Raymond Xie

**China Mobile IOT Company Limited**

Mr. Yuan Ding, Mr. Wei Li, Mr. Jiang Qiu, Ms. Shuangxue Ni

• Qorvo

Mr. Zhen Tao (Lawrence Tao)

Taiyo Yuden

Mr. Mike Tanahashi

• Murata

Mr. Xuan Zhang (Ken Zhang)

• Sunway

Mr. Qing Xu

• Anritsu

Mr. Bosco Choi

• Keysight

Ms. Isabel Rosa, Mr. Neil Payne, Ms. Deepa Karunanidhi

Rohde & Schwarz

Mr. Tim Wang

This whitepaper will be continuously updated according to the research and development progress.

### 5 The Standardization Status

### 5.1 Motivation

5G network provides the enhanced bandwidth and helps many applications improve their performance. For example, Virtual and Augmented Reality, UHD 8K Online 360 Video, 16K VR Head Mounted Display for game and training, Connected Drones, Connected Automotive, Wireless e-Health – Remote Surgery, Wireless home entertainment – smart home gateway, Live Radio/Video Broadcasting, Smart helmet, Always-connected PC/Tablet/2-in-1 PC, Real-time UHD Video Surveillance and Robots (See more in "GTI Report on Vertical Requirements for 5G S-Modules and Devices"). Thus, 5G devices could serve the users in a much better and efficient way. The key motivations are as follows:

- The available bandwidth for the applications will be substantial

- Data throughput will be increased along with enhanced connectivity, higher user mobility and higher accuracy positioning

- The 5G devices could use 5G S-Module and work out their solution efficiently

5G networks can support a large number of high bandwidth devices. 5G is power efficient. It delivers a long mobile battery life because it has been engineered and optimized to operate over an extended period. 5G NR network with eMBB provides high bandwidth for the 5G multi-mode multi-band modules and modem end-devices, thus it will be beneficial for the 5G device vendors. For example, ACPC vendors could use 5G S-Module in their device product and solution directly. Economies of scale arise because the capacity of S-Module suppliers is essentially shared around the GTI markets and at the 5G industry level. The quicker we bridge 5G chipsets to S-Module, the better GTI 5G device ecosystem develops. Currently every module vendor designs their own wireless modules, with different size, form factor and pin definition. This is an industry wide bottleneck and we intend to improve the situation.

User-centric authentication layer on top of the existing subscription authentication is introduced to share S-Module usage. Once 5G networks are deployed, different users can share limited kinds of 5G S-Module. To improve the user experience, it would be beneficial to automatically change settings of operator deployed services according to the users' settings. This requires the user to be identified in addition to the existing identification of subscription based off S-Module SIM. Network settings can be adapted and services offered to users according to their user identities, independent of the subscription that is used to establish the connection [TR22.904]. Using network resource slicing technology, application aware user experience could be delivered to all user identities shared the same S-Module gateway simultaneously [TR 23.727].

### 5.2 Standardization of 5G S-Module

### 5.2.1 The Diagram of 5G S-Module

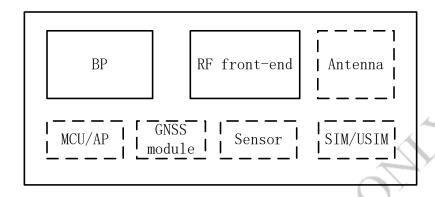

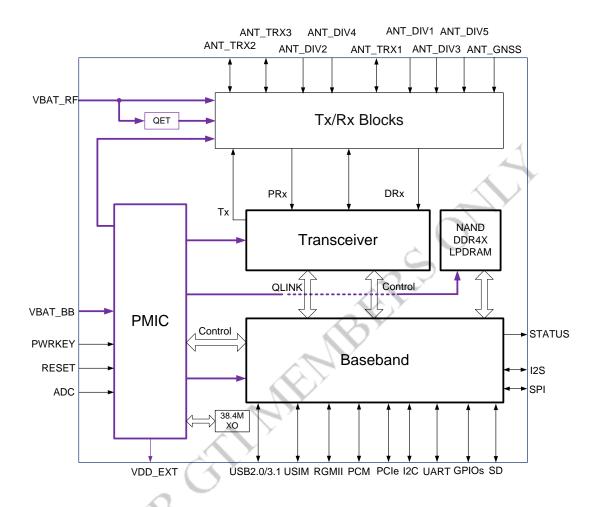

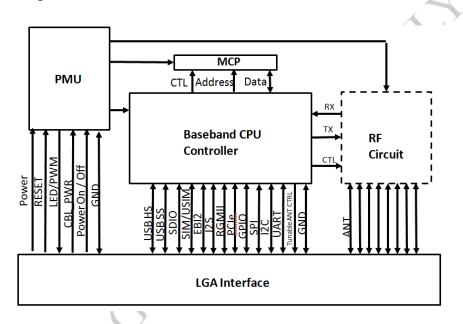

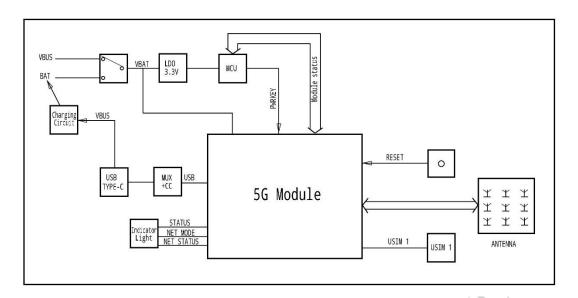

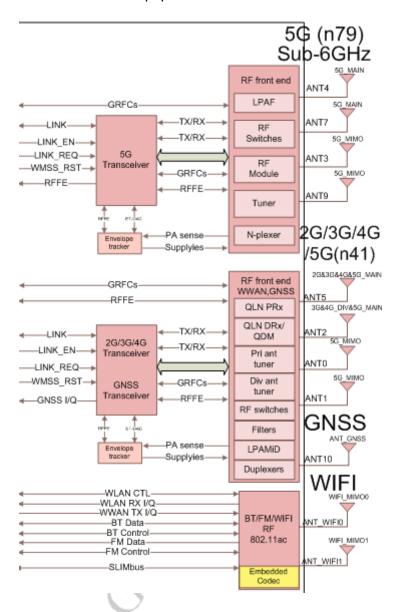

Figure 5-1 Diagram of 5G S-Module

Basic logical structure of 5G S-Module which is mainly composed of BP and RF front end is shown in Figure 5-1. 5G S-Module can also include antenna, MCU/AP, GNSS module, Sensor and SIM/USIM in terms of its different uses and functions.

### 5.2.2 The Key Points to classify 5G S-Module

To facilitate 5G device developments, we define modes, bands, data rate, size, form factor, weight, interface, AP/MCU, and antenna of the 5G S-Module. Considering requirements from different applications, 5G S-Modules have been divided into two major categories: Basic Type-L and Basic Type-M without high-performance processor, Smart Type with high-performance processor, Basic Type-L with LGA form factor, Basic Type-M with M.2 form factor, and All-in-one Type with built-in antennas.

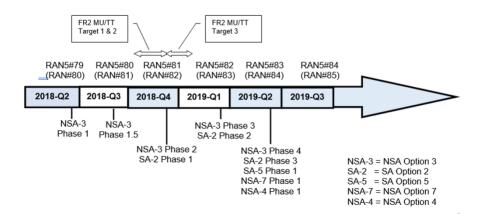

### 5.2.2.1 Modes and Bands

The 5G S-Module may be a series of modules, depending on how many modes and how many bands it supports. The modes and bands specification are as follows:

5G NR Bands:

Mandatory: n41, n79, n78

Optional: n77

LTE FDD Bands:

Mandatory: B7, B3, B8, B1, B2, B5, B25

Optional: B4, B12, B17, B20

TD-LTE Bands:

Mandatory: B34, B39, B40, B41

### 5.2.2.2 Data Rate

Date rate requested for 5G NR Sub 6GHz Module:

SA Mode:

1) DL peak rate: 1.7 Gbps

2) UL peak rate: 190 Mbps

Note: 5G NR bandwidth 100 MHz

### 5.2.2.3 Size and Form Factor

The 5G S-Module may be a series of modules, depending on different size.

1) Package Dimension (LGA):

LGA form factor module can be applied to most of the eMBB and IoT applications, such as CPE, STB, Laptop, Tablet, and Telematics. It is also the most widely used form factor in current 4G module industry.

2) Package Dimension (LGA+LCC)

LGA+LCC form factor module can be applied to almost all the applications for its flexibility, and sometimes it can greatly simplify the design of module and external applications.

3) Package Dimension (M.2):

M.2 form factor follows the definition of PCI Express M.2 Specification. It provides plug-in module solution for the end-device manufacturers.

### 5.2.2.4 Weight

Weight: less than 10g.

The consumer application such as AR/VR always prefer low weigh components. According to the weight of PCB, chips and other components in the module, the total weight of the 5G S-Module should be less than 10 g.

### 5.2.2.5 Interface

(U)SIM interface:

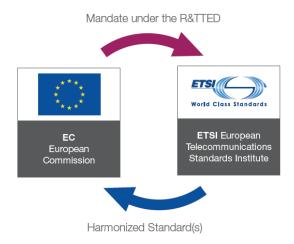

The (U)SIM interface circuitry meets ETSI and IMT-2000 requirements. Either 1.8 V or 3.0 V (U)SIM cards are supported.

### USB 3.1(Optional)/3.0/2.0 interface:

5G S-Module provides one integrated Universal Serial Bus (USB) interface which complies with the USB 3.1/3.0/2.0 specifications. It supports SuperSpeed+ (10 Gbps) on USB 3.1 Gen 2 (Optional), SuperSpeed (5 Gbps) on USB 3.0, High Speed (480 Mbps) and Full Speed (12 Mbps) modes on USB 2.0. The USB interface is used for AT command communication, data transmission, GNSS NMEA output, software debugging, firmware upgrade and so on.

### PCle interface:

5G S-Module includes a PCIe interface, which is compliant with PCI Express Specification Revision 3.0.

### • UART interface:

The module provides 3 UART interfaces: the main UART interface, the debug UART interface, and the BT UART interface.

### PCM and I<sup>2</sup>C interface:

5G S-Module supports audio communication via PCM digital interface and  $I^2C$  interface. We recommend to support at least one interface in the future revision of this whitepaper.

### 5.2.2.6 AP/MCU

The 5G S-Module may be a series of modules, depending on different computing capabilities.

- 1) Applications such as artificial intelligence demand that S-Module should provide high performance computing capability. Hence, the 5G S-Module used in these fields should include a processor running at 1.3 GHz or higher, more than 4 GB of RAM and 8 GB of ROM.

- 2) Applications such as router and gateway do not require that S-Module provide high performance computing capability. Hence, the 5G S-Module used in these fields should include a processor running at 800 MHz or higher, more than 2 GB of RAM and 4 GB of ROM.

### 5.2.2.7 Antenna

The plug and play devices such as USB Dongle Wireless Modem Stick demand built-in antennas, which should be included in the 5G S-Modules.

### 6 The Industry Status

This section studies the global cellular module industry status, market share, growth opportunity, key players and challenges.

### 6.1 The Industry Status of 4G Module

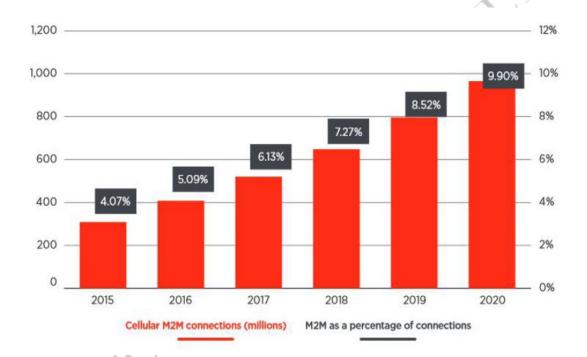

According to GSMA estimates, the number of cellular M2M connections in the world will reach 1 billion in 2020, with an average annual growth rate of 26.8%.

Figure 6-1 Forecast of global cellular M2M connections (From GSMA)

Cellular IoT modules are devices that allow for M2M connectivity across a variety of communication networks. The module is widely used in wireless POS, automobile, smart metering, connect laptop, CCTV, vehicle monitoring, remote control, telemetry, gateway, digital signage, vending machine, robot control, smart agriculture etc.

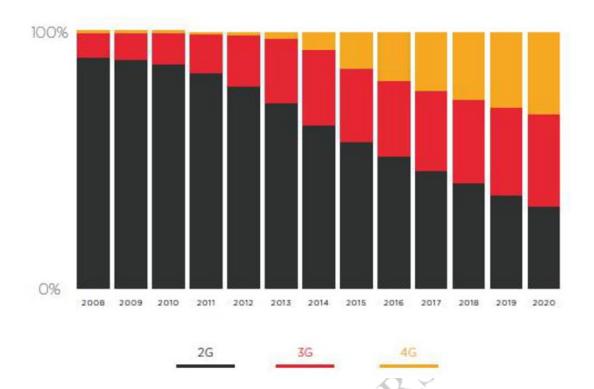

Industry application of cellular module is closely related to the construction of carriers' network. The commonly communication technologies are 2G,3G and 4G, some carries are also being deployed Cat.NB1 and Cat.M1 technologies. At the end of 2017, 644 public LTE networks have been deployed and have covered 200 countries/areas. With the evolution of carrier's network, more and more applications are switch to LTE modules from GSM/WCDMA modules.

Figure 6-2 Forecast of 2G/3G/4G M2M connections (From Ericsson)

The major module suppliers include Simcom, Fibocom, Quectel, Telit, Sierra wireless, Gemalto, U-Blox, ZTE Welink, Neoway etc.

Multiple application brings a fragmented LTE category application. Some use LTE Cat1 or Cat3 for replacing 3G technology because of carrier network upgrade, some use LTE Cat4 for better network coverage in these five years like china national grid, some use LTE Cat6 or Cat9 for better downlink data throughput, and some use Cat16 or above for both downlink and uplink, also for pre-5G research.

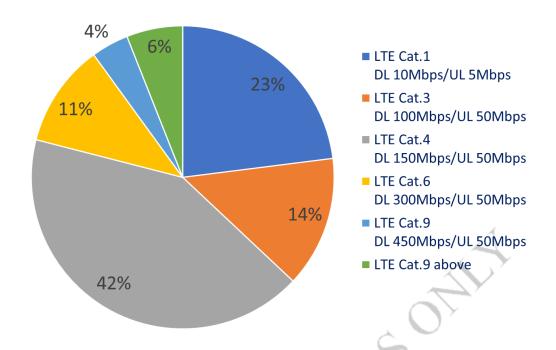

Figure 6-3 Percentage of different LTE category (From CMCC)

That also brings different kinds of module dimension in the market. There are standard interfaces like mini-PCIe and M.2, and other private definition interfaces. There are the different form factors like LCC, LGA, LCC+LGA. Even the same form factor module has different dimension and different pin definition between different module vendors.

Figure 6-4 Different form factor of LTE module (From public data)

### 6.2 How to make 5G S-Module?

The upstream of the cellular module is vendors of the standardized baseband chip, and the downstream is the application of industry.

The requirement of 5G S-Module will focus on the eMBB application.

The R&D of cellular module need to have strong communication technology, signal processing technology, information processing technology and other professional development capabilities, and need to have a strong protocol knowledge, OS drivers, embedded software development capabilities.

### 6.3 The Industry Status of 5G Chipset

Due to the prospect of 5G, the main manufacturers are constantly pushing forward the development process of chip products. According to the GSA report and news released by the companies, the announced 5G chipsets are summarized as follows:

- Hi-Silicon (Huawei): the first generation 5G-only Balong 5G01 cellular modem, the second generation LTE/5G Balong 5000 cellular modem, and the 5G version processor Kirin 990.

- Intel: the XMM8060 and XMM8160 cellular modems. [Note: Intel has confirmed its withdrawal from the 5G mobile modem market. Its previously announced XMM8060 and XMM8160 cellular modems will not be produced.] Mediatek: the Helio M70 modem and the multi-mode 5G SoC with Helio M70 modem built-in.

- Qualcomm: the Snapdragon 855 mobile platform, the Snapdragon X50 and X55 modems, and the 8cx 5G platform for laptops.

- Samsung: the Exynos 5100 (S5T5100) modem and the first 5G-integrated mobile processor Exynos 980.

- UNISOC: the 5G technology platform MAKALU and its first 5G Modem IVY510.

- U-Blox: the 5G-upgradeable IoT chipset UBX-R5, which will in the future be (but is not currently) capable of supporting 5G with an OTA software upgrade.

Regarding the performance of above listed 5G chipsets, the peak downlink speeds for the commercial modems range from 4.7 Gbps to 6.5 Gbps (Qualcomm's Snapdragon X55 is expected to have a peak theoretical throughput of 7 Gbps). The maximum peak theoretical uplink speeds range from 1.5 Gbps to 3.5 Gbps (from available data). In addition, at least half the commercially available 5G-capable chipsets can support LTE as well as 5G services.

### 6.4 The Industry Status of 5G Module

The mainstreaming module vendors have started developing 5G modules based on available 5G chipsets. According to the GSA report released in September 2019,

- 28 5G modules have been announced by 11 vendors.

- **19** 5G modules are developed based on Qualcomm Snapdragon X55 modem, **one** 5G module based on Huawei Balong 5000 modem, **one** to be confirmed, and **7** with no data.

- 17 5G modules support Sub-6GHz only, 7 5G modules support both Sub-6GHz and mmWave, and 4 with no data.

- **3** 5G modules are designed for IoV, i.e. Internet of Vehicle.

Most of the announced 5G modules are considered to be at a pre-commercial stage. Some modules are available for sampling and commercially available in 2020.

### 6.5 The Industry Status of 5G Device

Since the beginning of 2019, the number of 5G devices has grown quickly. According to the GSA report, by 10 September 2019,

- **56** vendors have announced available or forthcoming 5G devices, including sub-brands separately.

- 129 5G devices in 15 form factors have been announced, including 41 phones, 28 indoor/outdoor CPE devices, 28 modules, 9 hotspots, 4 routers, 3 robots, 3 televisions, 2 USB terminals/dongles, 2 snap-on dongles/adapters, 2 IoT routers, 2 drones, 2 head-mounted displays, one laptop, one switch, and one vending machine.

- Some of the announced 5G devices have been commercially available, while more

devices are in the phase of pre-commercial, sampling, or availability unknown.

## 7 The Basic functions Requirements on 5GS-Module

### 7.1 Management Functions

### 7.1.1 Identity Management

5G S-Module should have module identity. The module identity could be IMEI or IMSI on user card.

### 7.1.2 Status Management

5G S-Module should have capability of status management. It could be achieved by interface to indicate module working status.

### 7.1.3 Parameter Preset Management

5G S-Module should be preset for cellular network bearer access parameters, including but not limited to APN, SMS center number, IP(or URL) and port number.

### 7.2 SIM Functions

5G S-Module should support one or more of pluggable SIM/USIM/CSIM interface, SMD type SIM/USIM/CSIM (eUICC) and other SIM form. The following table shows the pins of pluggable SIM/USIM/CSIM. One of two voltage levels should be supported: 3V±10% or 1.8V±10%.

Interface **Interface Description** Interface Name Interface Type Characteristics SIM USIM\_DETECT **USIM DETECT Signal** I interface USIM\_RESET **USIM RESET Signal** 0 USIM\_CLK **USIM CLK Signal** O 1/0 USIM\_DATA **USIM DATA Signal** USIM\_VCC **USIM Power Output** 0

Table 7-1 (U)SIM Interface

### 7.3 Debug Functions

The 5G S-Module needs to support developing debug log, opening and closing debug log and outputting debug log via UART or USB or SPI interface.

### 7.4 Firmware Upgrade Functions

The 5G S-Module should support secured firmware upgrade. The firmware of 5G S-Module could be upgraded by FOTA. The implementation of firmware upgrade depends on device implementation.

The update workflow includes FOTA initializing, downloading update package segment, getting FOTA update result, getting package name, getting package version and firmware upgrading.

# 8 The Hardware Technical Requirements on 5G S-Module

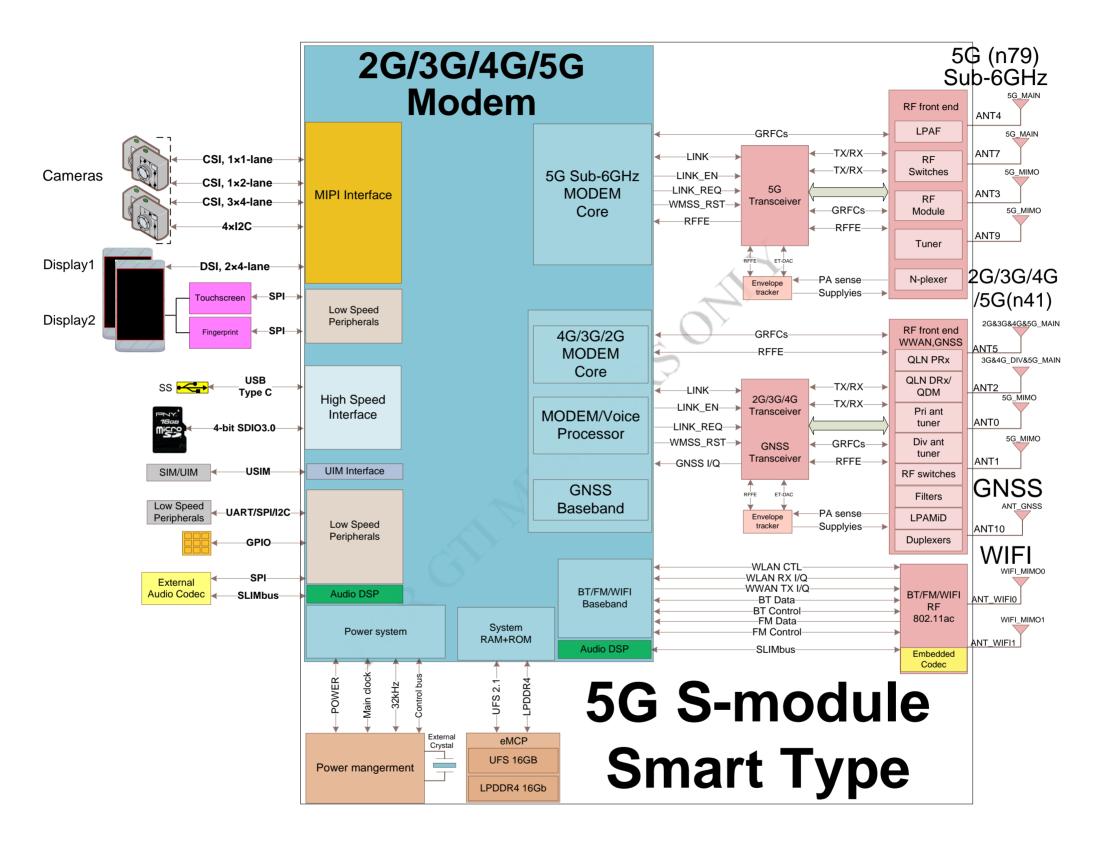

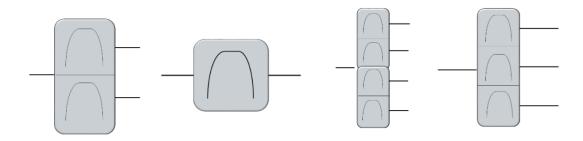

Basing on variety of characteristics, form factor, sizes, etc, the 5G S-Module could be classified into 3 types shown below: Basic Type, Smart Type and All-in-one Type.

| Туре            | Basic Type                                | Smart Type                             | All-in-one Type            |  |  |

|-----------------|-------------------------------------------|----------------------------------------|----------------------------|--|--|

| Characteristics | Only communication capability             | High performance Application Processor | Built-in antennas          |  |  |

| Form Factor     | LGA and M.2                               | LCC+LGA                                | Dongle                     |  |  |

| Size            | ≤ 41mm*44mm<br>≤ 42mm*42mm<br>≤ 30mm*52mm | ≤ 44mm*45mm                            | ≤ 52mm*93mm<br>≤ 44mm*70mm |  |  |

| FORCHILM        |                                           |                                        |                            |  |  |

### 8.1 5G S-Module Basic Type-L

### 8.1.1 Diagram

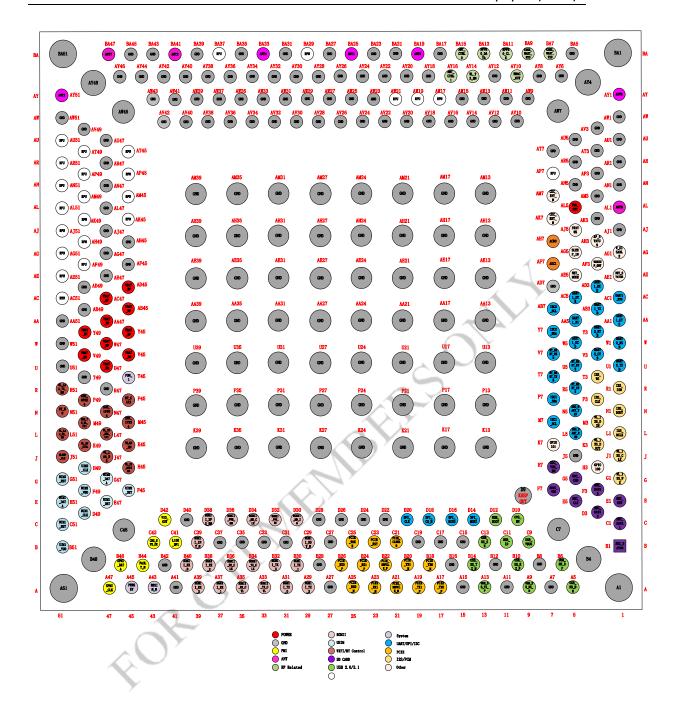

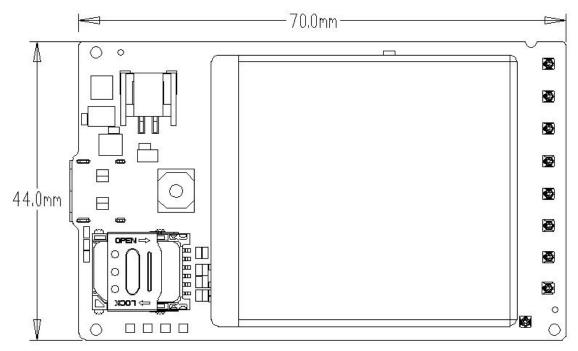

Figure 8-1 5G S-Module Basic Type-L Diagram

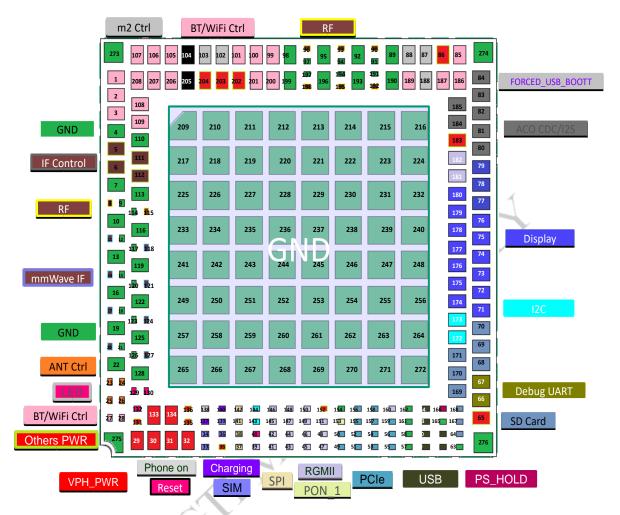

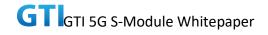

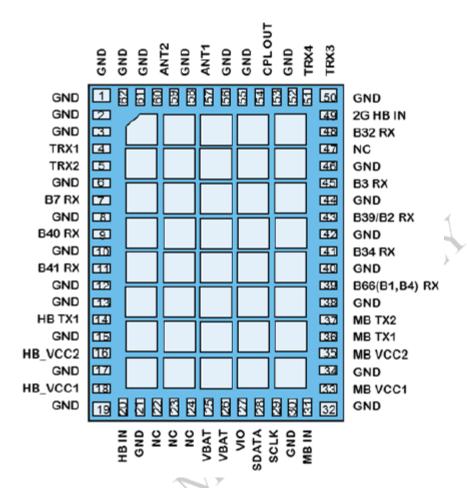

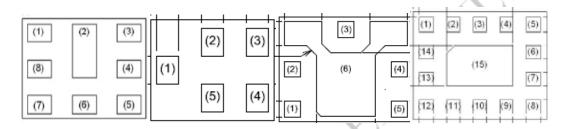

### 8.1.2 Pin Layout

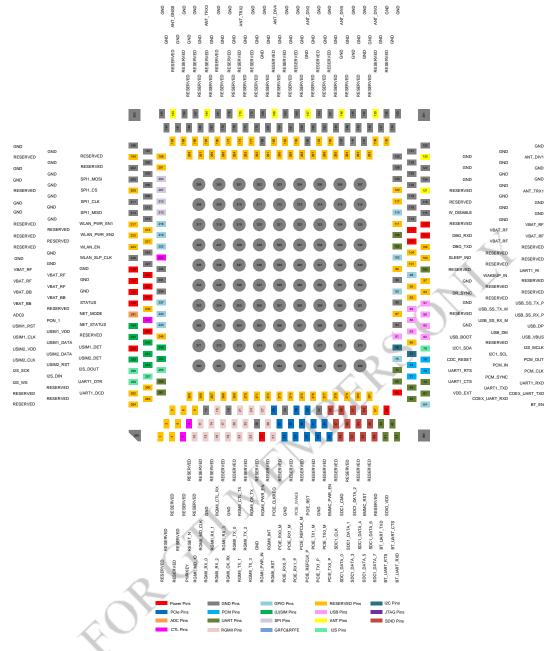

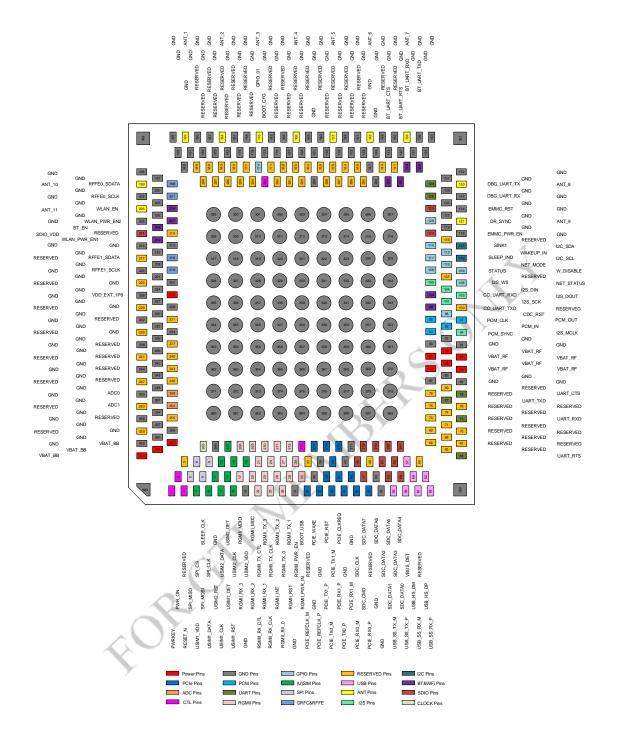

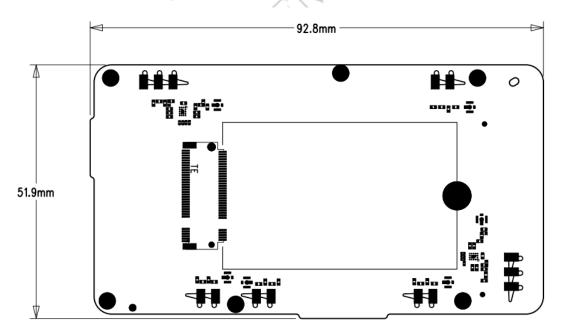

Figure 8-2 5G S-Module Basic Type-L Pin Layout-1

Figure 8-2A 5G S-Module Basic Type-L Pin Layout-2

Figure 8-2B 5G S-Module Basic Type-L Pin Layout-3

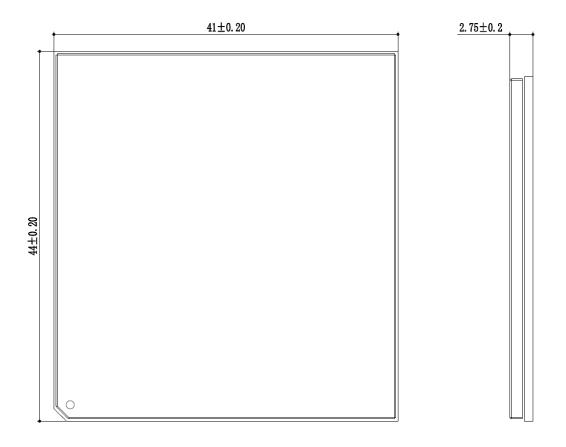

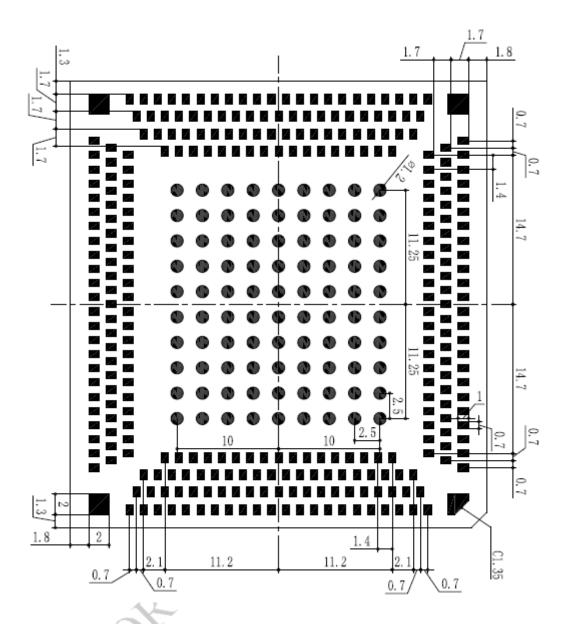

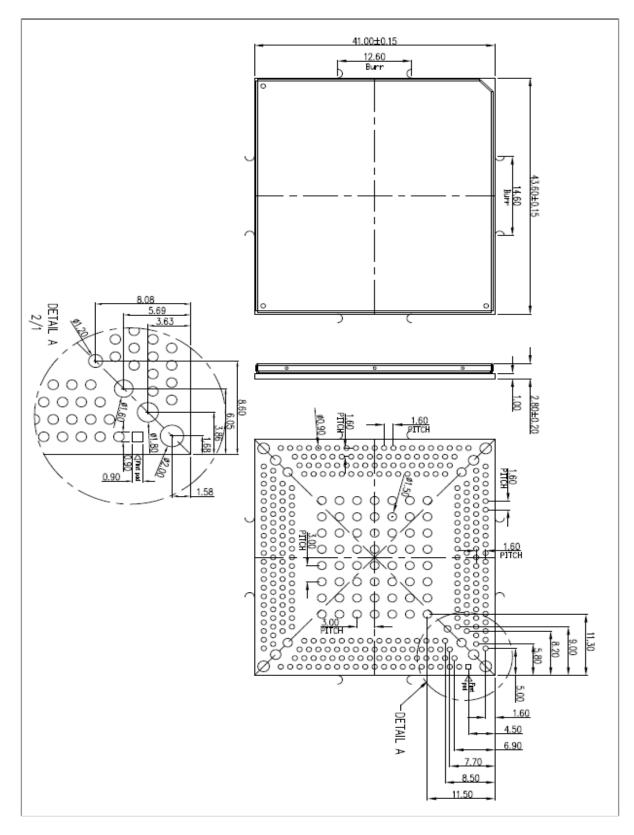

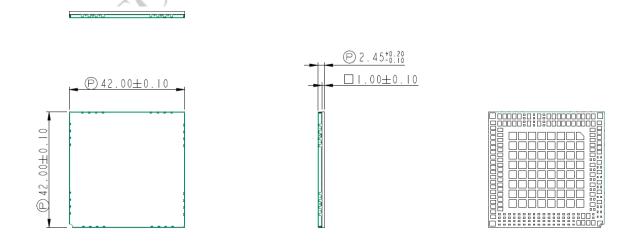

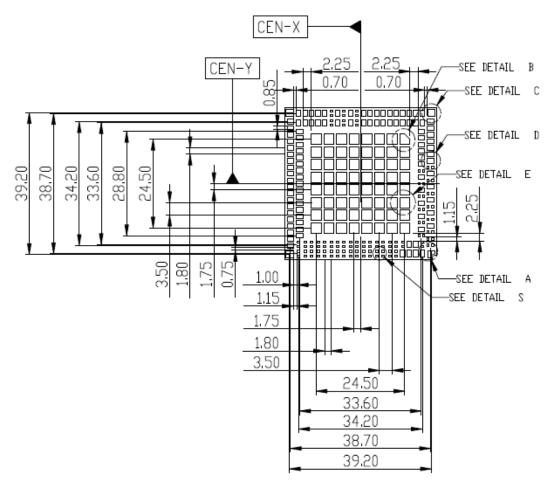

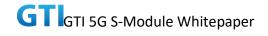

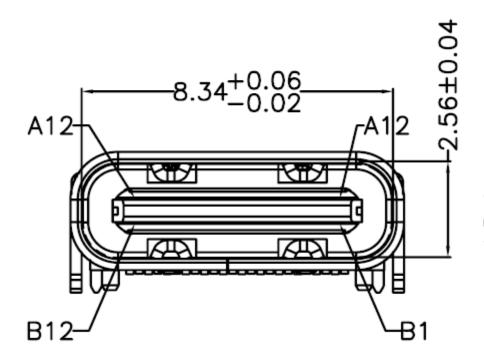

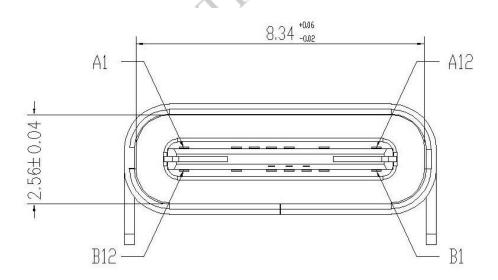

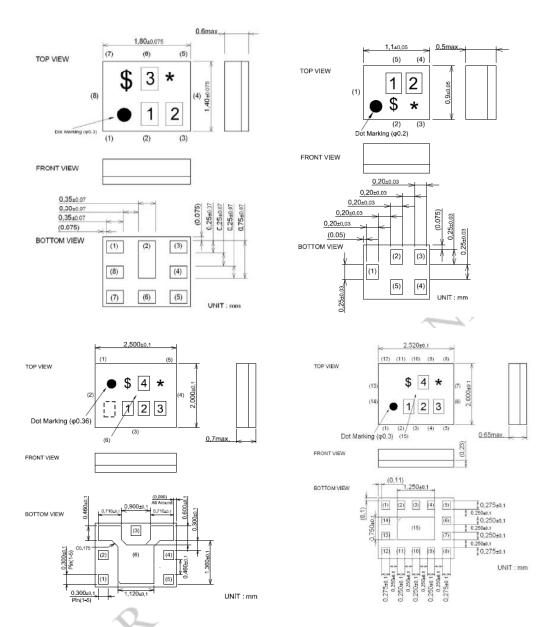

### 8.1.3 Pin Size

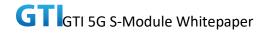

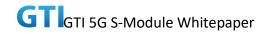

Top View Side View

Figure 8-3 5G S-Module Basic Type-L Pin Size (Layout-1 and Layout-2)

Figure 8-3A 5G S-Module Basic Type-L Pin Size (Layout-3)

### 8.1.4 Pin Definition

Table 8-1 5G S-Module Basic Type-L Pin Definition(Layout-1)

| Pin name         | Pin No.                                      | Default<br>status | Description                                                                                | Comment                            |

|------------------|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------|------------------------------------|

| Power supply     |                                              | Status            |                                                                                            |                                    |

| VBAT_BB          | 235,236,2<br>38                              | PI                | Baseband power supply.                                                                     | Can connect these pins             |

| VBAT_RF          | 107,109,<br>110,112,<br>,229,230,<br>232,233 | PI                | RF power supply.                                                                           | together to the same power source. |

| VDD_EXT          | 66                                           | РО                | 1.8 output with Max 50mA current output for external circuit, such as level shift circuit. | If unused, please keep it open.    |

| System Control   |                                              |                   |                                                                                            |                                    |

| PWRKEY           | 7                                            | DI                | System power on/off control input, active low.                                             |                                    |

| PON_1            | 242                                          | DI                | Pull it to high level will make the module turn on automatically.                          |                                    |

| RESET            | 8                                            | DI                | System reset control input, active low.                                                    |                                    |

| Status Indicator |                                              |                   |                                                                                            |                                    |

| STATUS           | 237                                          | DO                | System status output                                                                       |                                    |

| NET_MODE         | 240                                          | DO                | Network Mode output                                                                        |                                    |

| NET_STATUS       | 243                                          | DO                | Network status output                                                                      |                                    |

| USB interface    |                                              |                   |                                                                                            |                                    |

| USB_VBUS         | 82                                           | Al                | USB detection input.                                                                       |                                    |

| USB_DP           | 85                                           | AIO               | Positive line of the differential, bi-directional USB signal.                              | If unused, please keep             |

| USB_DM           | 83                                           | AIO               | Negative line of the differential, bi-directional USB signal.                              | them open.                         |

| USB_BOOT         | 81                                           | DI                | Force the module to boot from USB port                                                     |                                    |

| USB_SS_ TX_P     | 91  | AO  | USB Super-Speed transmit – plus                                    |                                             |

|------------------|-----|-----|--------------------------------------------------------------------|---------------------------------------------|

| USB_SS_ TX_M     | 89  | AO  | USB Super-Speed transmit – minus                                   |                                             |

| USB_SS_ RX_P     | 88  | Al  | USB Super-Speed receive – plus                                     |                                             |

| USB_SS_ RX_M     | 86  | Al  | USB Super-Speed receive – minus                                    |                                             |

| (U)SIM interface |     |     |                                                                    |                                             |

| USIM1_VDD        | 245 | PO  | Power supply for (U)SIM card1                                      |                                             |

| USIM1_DATA       | 248 | DIO | Data signal of (U)SIM card1                                        | 1.8V or 2.85V power domain                  |

| USIM1_CLK        | 247 | DO  | USIM1 clock output                                                 |                                             |

| USIM1_RST        | 244 | DO  | USIM1 Reset output                                                 |                                             |

| USIM1_DET        | 249 | DI  | USIM1 card detecting input. H: USIM is removed L: USIM is inserted | 1.8V power domain. If unused, keep it open. |

| USIM2_VDD        | 250 | PO  | Power supply for (U)SIM card2                                      |                                             |

| USIM2_DATA       | 251 | DIO | Data signal of (U)SIM card2                                        | 1.8V or 2.85V power domain                  |

| USIM2_CLK        | 253 | DO  | Clock signal of (U)SIM card2                                       |                                             |

| USIM2_RST         | 254 | DO | Reset signal of (U)SIM card2                                             |                                             |

|-------------------|-----|----|--------------------------------------------------------------------------|---------------------------------------------|

| USIM2_DET         | 252 | DI | USIM2 card detecting input.<br>H: USIM is removed<br>L: USIM is inserted | 1.8V power domain. If unused, keep it open. |

| SPI interface     |     |    |                                                                          |                                             |

| SPI1_CS           | 207 | DO | SPI chip select                                                          |                                             |

| SPI1_CLK          | 210 | DO | SPI clock                                                                |                                             |

| SPI1_MOSI         | 204 | DO | Master output slaver input                                               |                                             |

| SPI1_MISO         | 213 | DI | Master input slaver output                                               |                                             |

| UART1 interface   | _   | _  |                                                                          |                                             |

| UART1_RI          | 100 | DO | Ring Indicator                                                           |                                             |

| UART1_DCD         | 261 | DO | Data carrier detectsion                                                  |                                             |

| UART1_CTS         | 69  | DO | Clear to Send                                                            |                                             |

| UART1_RTS         | 72  | DI | Request to send                                                          | If unused, please keep them open.           |

| UART1_DTR         | 258 | DI | Data Terminal Ready,sleep<br>mode control                                |                                             |

| UART1_TXD         | 68  | DO | Transmit Data                                                            |                                             |

| UART1_RXD         | 70  | DI | Receive Data                                                             |                                             |

| Debug interface   |     |    |                                                                          |                                             |

| DBG_RXD           | 108 | DI | Debug UART receive Data                                                  | If unused, please keep                      |

| DBG_TXD           | 105 | DO | Debug UART transmit Data                                                 | them open.                                  |

| BT UART interface |     |    |                                                                          |                                             |

| BT_UART_TXD    | 59  | DO  | BT UART Transmit Data     |                                                   |

|----------------|-----|-----|---------------------------|---------------------------------------------------|

| BT_UART_RXD    | 63  | DI  | BT UART Receive Data      | If unused, please keep                            |

| BT_UART_RTS    | 61  | DI  | BT UART Request to send   | them open.                                        |

| BT_UART_CTS    | 62  | DO  | BT UART Clear to Send     |                                                   |

| ADC interface  |     |     |                           |                                                   |

| ADC0           | 241 | Al  | ADC input                 | If unused, please keep them open.                 |

| PCM interface  |     |     |                           |                                                   |

| PCM_IN         | 74  | DI  | PCM data input            |                                                   |

| PCM_OUT        | 76  | DO  | PCM data output           | If unused, please keep                            |

| PCM_SYNC       | 71  | DIO | PCM synchronous signal    | them open.                                        |

| PCM_CLK        | 73  | DIO | PCM clock output          |                                                   |

| I2S interface  |     |     |                           |                                                   |

| 12S_WS         | 259 | DIO | I2S word select           |                                                   |

| I2S_SCK        | 256 | DIO | I2S bit clock             | 1.8V power domain                                 |

| I2S_DIN        | 257 | DI  | I2S data input            | 1.6V power domain                                 |

| I2S_DOUT       | 255 | DO  | I2S data output           |                                                   |

| I2C interface  |     |     |                           |                                                   |

| I2C1_SCL       | 77  | OD  | I2C clock output          | OD gate driver, pull-up resistors of 2.2KR to the |

| I2C1_SDA       | 78  | OD  | I2C data input/output     | VDD_1V8 are needed.  If unused, please keep open  |

| PCIE interface |     |     |                           |                                                   |

| PCIE_REFCLK_P  | 40  | AO  | PCIe reference clock plus | If unused, please keep them open.                 |

| PCIE_REFCLK_M    | 38  | АО  | PCIe reference clock minus |                        |

|------------------|-----|-----|----------------------------|------------------------|

| PCIE_TX0_M       | 44  | AO  | PCIe Lane 0 transmit minus |                        |

| PCIE_TX0_P       | 46  | AO  | PCIe Lane 0 transmit plus  |                        |

| PCIE_RXO_M       | 32  | Al  | PCIe Lane 0 receive minus  |                        |

| PCIE_RXO_P       | 34  | Al  | PCIe Lane 0 receive plus   |                        |

| PCIE_TX1_M       | 41  | AO  | PCIe Lane 1 transmit minus |                        |

| PCIE_TX1_P       | 43  | АО  | PCIe Lane 1 transmit plus  |                        |

| PCIE_RX1_M       | 35  | Al  | PCIe Lane 1 receive minus  |                        |

| PCIE_RX1_P       | 37  | Al  | PCIe Lane 1 receive plus   |                        |

| PCIE_CLKREQ      | 30  | DIO | PCIe clock request         |                        |

| PCIE_RST         | 39  | DIO | PCIe reset                 |                        |

| PCIE_WAKE        | 36  | DIO | PCIe wake-up host          |                        |

| WLAN interface   |     |     |                            |                        |

| WLAN_PWR_<br>EN1 | 216 | DO  | WLAN power enable1         |                        |

| WLAN_PWR_<br>EN2 | 219 | DO  | WLAN power enable2         |                        |

| WAKE_SLP_CLK     | 225 | DO  | WLAN sleep clock           | If unused, please keep |

| WLAN_EN          | 222 | DO  | WLAN function enable       | them open.             |

| COEX_UART_ RXD   | 65  | DI  | Coex UART Receive data     |                        |

| COEX_UART_TXD    | 67  | DO  | Coex UART Transmit data    |                        |

| SD interface     |     |     |                            |                        |

42

| SDIO_VDD        | 60 | PI  | Power supply of SDIO data signal |                            |

|-----------------|----|-----|----------------------------------|----------------------------|

| SDC1_DATA0      | 49 | DIO | SDIO data 0                      |                            |

| SDC1_DATA1      | 50 | DIO | SDIO data 1                      |                            |

| SDC1_DATA2      | 51 | DIO | SDIO data 2                      |                            |

| SDC1_DATA3      | 52 | DIO | SDIO data 3                      |                            |

| SDC1_CMD        | 48 | DO  | SDIO command output              | 1.8V or 2.85V power domain |

| SDC1_CLK        | 47 | DO  | SDIO clock output                |                            |

| SDC1_DATA4      | 53 | DIO | SDIO data 4                      |                            |

| SDC1_DATA5      | 55 | DIO | SDIO data 5                      |                            |

| SDC1_DATA6      | 56 | DIO | SDIO data 6                      |                            |

| SDC1_DATA7      | 58 | DIO | SDIO data 7                      |                            |

| EMMC_RST        | 54 | DO  | Reset signal for eMMC flash      |                            |

| EMMC_PWR_EN     | 45 | DO  | Enable eMMC power supply         |                            |

| RGMII interface |    |     |                                  |                            |

| RGMII_MD_IO     | 10 | DIO | RGMII MDIO management data       |                            |

| RGMII_MD_CLK    | 11 | DO  | RGMII MDC management clock       |                            |

| RGMII_RX_0      | 13 | DI  | RGMII receive data bit 0         |                            |

| RGMII_RX_1   | 14  | DI    | RGMII receive data bit 1                                         |                   |

|--------------|-----|-------|------------------------------------------------------------------|-------------------|

| RGMII_CTL_RX | 15  | DI    | RGMII receive control                                            |                   |

| RGMII_RX_2   | 16  | DI    | RGMII receive data bit 2                                         |                   |

| RGMII_RX_3   | 17  | DI    | RGMII receive data bit 3                                         |                   |

| RGMII_CK_RX  | 19  | DI    | RGMII receive clock                                              |                   |

| RGMII_TX_0   | 20  | DO    | RGMII transmit data bit 0                                        |                   |

| RGMII_CTL_TX | 21  | DO    | RGMII transmit control                                           |                   |

| RGMII_TX_1   | 22  | DO    | RGMII transmit data bit 1                                        |                   |

| RGMII_TX_2   | 23  | DO    | RGMII transmit data bit 2                                        |                   |

| RGMII_CK_TX  | 24  | DO    | RGMII transmit clock                                             |                   |

| RGMII_TX_3   | 25  | DO    | RGMII transmit data bit 3                                        |                   |

| RGMII_PWR_EN | 27  | DO    | Used to enable external LDO to supply 2.5V power to RGMII_PWR_IN | 1.8V power domain |

| RGMII_PWR_IN | 28  | PI    | Power input for internal RGMII circuit                           |                   |

| RGMII_INT    | 29  | DI    | RGMII PHY interrupt output                                       | 1.8V power domain |

| RGMII_RST    | 31  | DO    | Reset output for RGMII PHY                                       | 1.0V power domain |

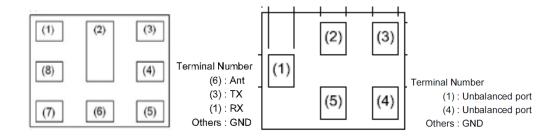

| RF interface |     |       |                                                                  |                   |

| ANT_TRX2     | 175 | AI/AO | Main antenna2, support TX and RX                                 |                   |

| ANT_TRX3  | 184 | AI/AO | Main antenna3, support TX and RX |  |

|-----------|-----|-------|----------------------------------|--|

| ANT_DIV2  | 157 | AI    | Diversity receive antenna 2      |  |

| ANT_DIV4  | 166 | Al    | Diversity receive antenna 4      |  |

| ANT_TRX1  | 121 | AI/AO | Main antenna1, support TX and RX |  |

| ANT_DIV1  | 130 | Al    | Diversity receive antenna 1      |  |

| ANT_DIV3  | 139 | AI    | Diversity receive antenna 3      |  |

| ANT_DIV5  | 148 | Al    | Diversity receive antenna 5      |  |

| ANT_GNSS  | 193 | Al    | GNSS antenna interface           |  |

| GPIO      |     |       |                                  |  |

| WAKEUP_IN | 98  | DI    | Sleep Mode control               |  |

| W_DISABLE | 114 | DI    | Flight Mode control              |  |

| SLEEP_IND | 102 | DO    | Indicating module sleep status   |  |

| Others    |     |       |                                  |  |

| BT_EN     |     |       |                                  |  |

| CDC_RESET | 75  | DO    | Reset of codec                   |  |

| I2S_MCLK  | 79  | DO    | Clock output                     |  |

| DR_SYNC   | 93  | DO    | Navigation 1PPS time sync output |  |

| GND       |     |       |                                  |  |

| GND       |     |       |                                  |  |

| RESERVED  |     |       |                                  |  |

RESERVED

Table 8-1A 5G S-Module Basic Type-L Pin Definition(Layout-2)

| Pin name       | Pin No.               | Default status | Description                                                                                | Comment                                     |  |  |

|----------------|-----------------------|----------------|--------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| Power supply   | Power supply          |                |                                                                                            |                                             |  |  |

| VBAT_BB        | 264,263,2<br>61       | PI             | Baseband power supply.                                                                     | Can connect these pins together to the same |  |  |

| VBAT_RF        | 88,85,89,8<br>6,87,84 | PI             | RF power supply.                                                                           | power source.                               |  |  |

| VDD_EXT_1V8    | 225                   | РО             | 1.8 output with Max 50mA current output for external circuit, such as level shift circuit. | If unused, please keep it open.             |  |  |

| System Control |                       |                |                                                                                            |                                             |  |  |

| PWRKEY         | 1                     | DI             | System power on/off control input, active low.                                             |                                             |  |  |

| PWR_ON         | 2                     | DI             | Pull it to high level will make the module turn on automatically.                          |                                             |  |  |

| BOOT_CFG       | 293                   | DI             | Module boot config                                                                         |                                             |  |  |

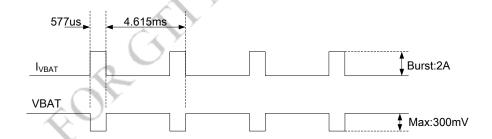

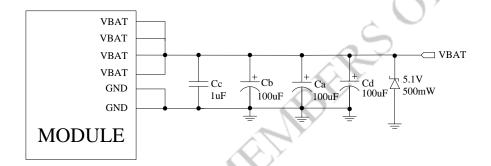

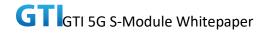

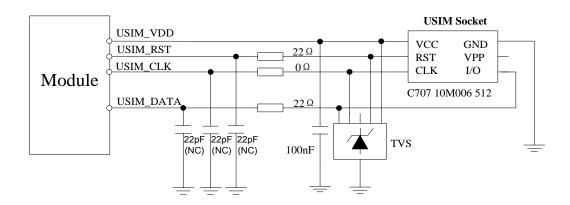

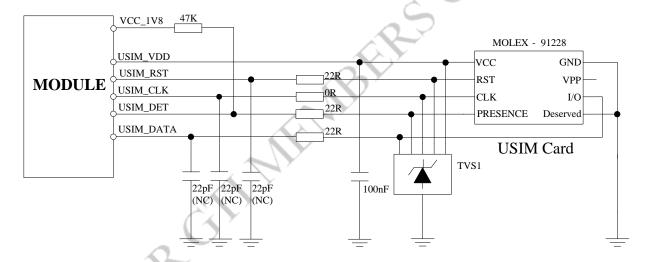

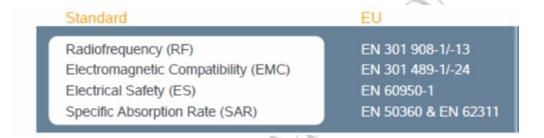

| BOOT_USB       | 273                   | DI             | Force the module to boot from USB port                                                     |                                             |  |  |